Wiley Series on Parallel and Distributed Computing • Albert Zomaya, Series Editor

# ALGORITHMS AND PARALLEL COMPUTING

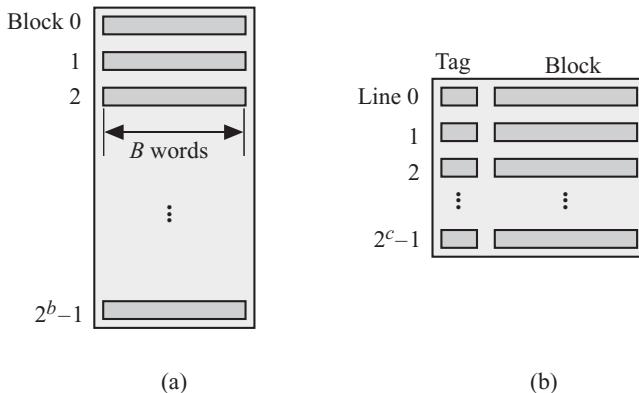

FAYEZ GEBALI

WILEY

# **Algorithms and Parallel Computing**

# Algorithms and Parallel Computing

**Fayez Gebali**

*University of Victoria, Victoria, BC*

A John Wiley & Sons, Inc., Publication

Copyright © 2011 by John Wiley & Sons, Inc. All rights reserved

Published by John Wiley & Sons, Inc., Hoboken, New Jersey Published simultaneously in Canada

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at [www.copyright.com](http://www.copyright.com). Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at <http://www.wiley.com/go/permission>.

**Limit of Liability/Disclaimer of Warranty:** While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at [www.wiley.com](http://www.wiley.com).

Library of Congress Cataloging-in-Publication Data

Gebali, Faye.

Algorithms and parallel computing/Faye Gebali.

p. cm.—(Wiley series on parallel and distributed computing ; 82)

Includes bibliographical references and index.

ISBN 978-0-470-90210-3 (hardback)

1. Parallel processing (Electronic computers) 2. Computer algorithms. I. Title.

QA76.58.G43 2011

004'.35—dc22

2010043659

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

*To my children: Michael Monir, Tarek Joseph,

Aleya Lee, and Manel Alia*

# Contents

---

**Preface**      xiii

**List of Acronyms**      xix

---

|          |                     |          |

|----------|---------------------|----------|

| <b>1</b> | <b>Introduction</b> | <b>1</b> |

|----------|---------------------|----------|

---

|      |                                                       |    |

|------|-------------------------------------------------------|----|

| 1.1  | Introduction                                          | 1  |

| 1.2  | Toward Automating Parallel Programming                | 2  |

| 1.3  | Algorithms                                            | 4  |

| 1.4  | Parallel Computing Design Considerations              | 12 |

| 1.5  | Parallel Algorithms and Parallel Architectures        | 13 |

| 1.6  | Relating Parallel Algorithm and Parallel Architecture | 14 |

| 1.7  | Implementation of Algorithms: A Two-Sided Problem     | 14 |

| 1.8  | Measuring Benefits of Parallel Computing              | 15 |

| 1.9  | Amdahl's Law for Multiprocessor Systems               | 19 |

| 1.10 | Gustafson–Barsis's Law                                | 21 |

| 1.11 | Applications of Parallel Computing                    | 22 |

---

|          |                                           |           |

|----------|-------------------------------------------|-----------|

| <b>2</b> | <b>Enhancing Uniprocessor Performance</b> | <b>29</b> |

|----------|-------------------------------------------|-----------|

---

|     |                                                                |    |

|-----|----------------------------------------------------------------|----|

| 2.1 | Introduction                                                   | 29 |

| 2.2 | Increasing Processor Clock Frequency                           | 30 |

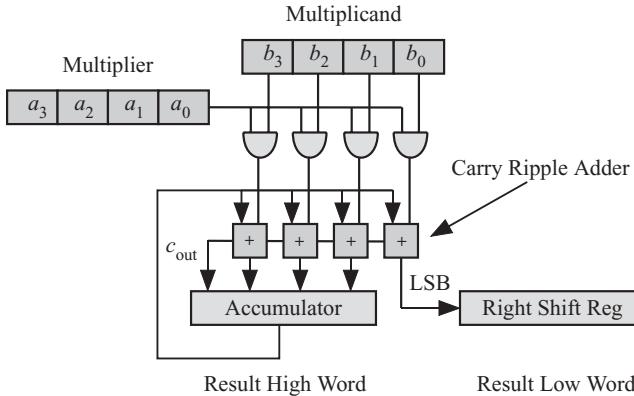

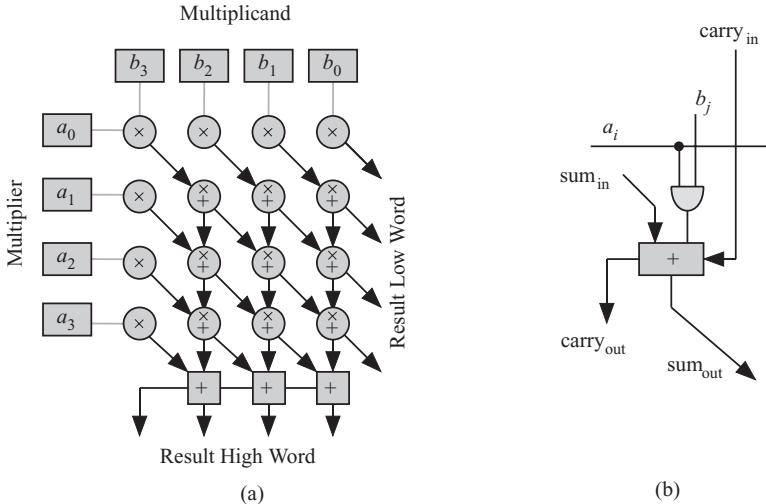

| 2.3 | Parallelizing ALU Structure                                    | 30 |

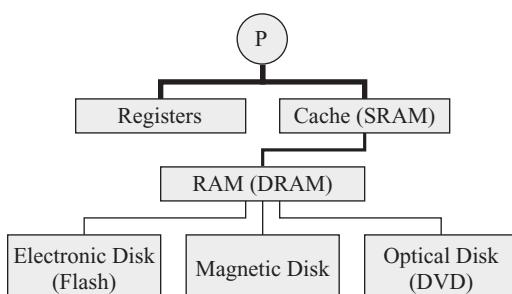

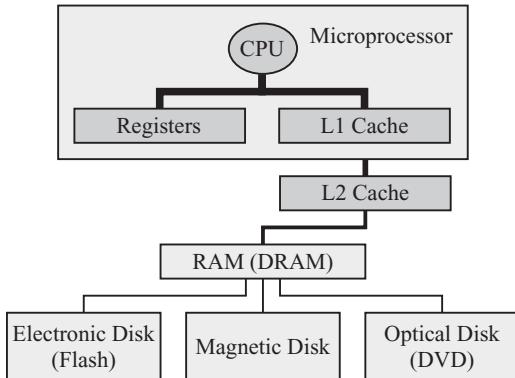

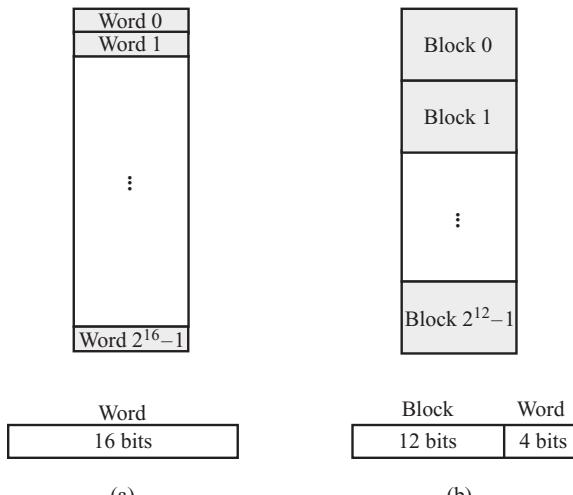

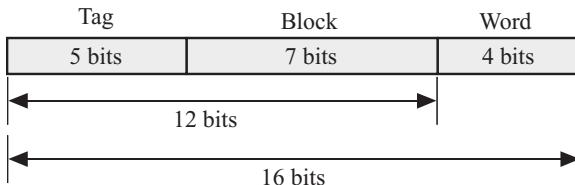

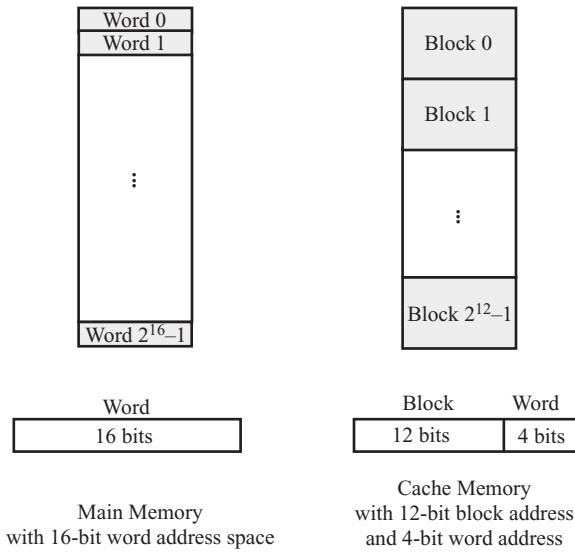

| 2.4 | Using Memory Hierarchy                                         | 33 |

| 2.5 | Pipelining                                                     | 39 |

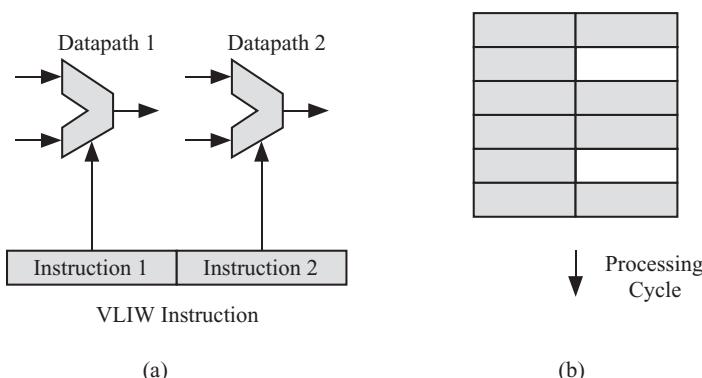

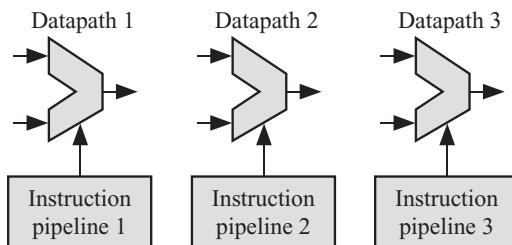

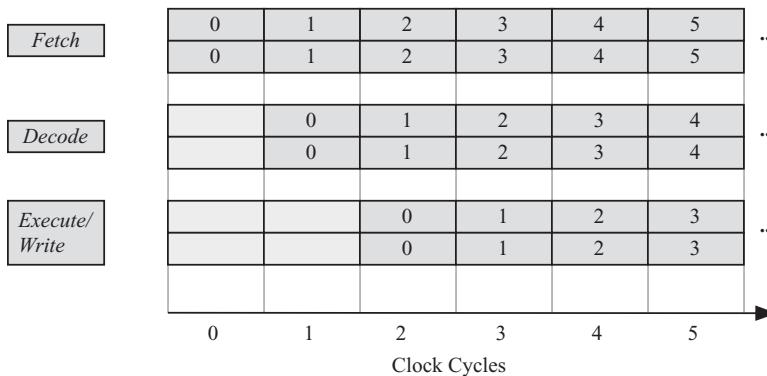

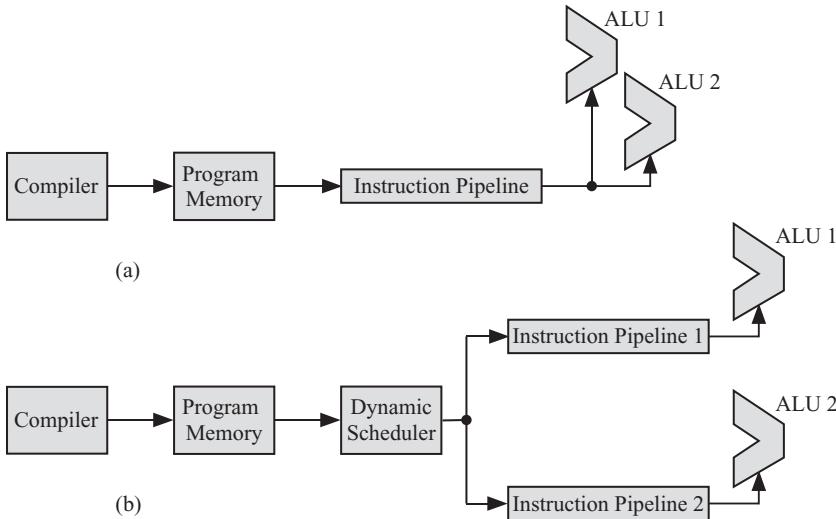

| 2.6 | Very Long Instruction Word (VLIW) Processors                   | 44 |

| 2.7 | Instruction-Level Parallelism (ILP) and Superscalar Processors | 45 |

| 2.8 | Multithreaded Processor                                        | 49 |

---

|          |                           |           |

|----------|---------------------------|-----------|

| <b>3</b> | <b>Parallel Computers</b> | <b>53</b> |

|----------|---------------------------|-----------|

---

|     |                                                                     |    |

|-----|---------------------------------------------------------------------|----|

| 3.1 | Introduction                                                        | 53 |

| 3.2 | Parallel Computing                                                  | 53 |

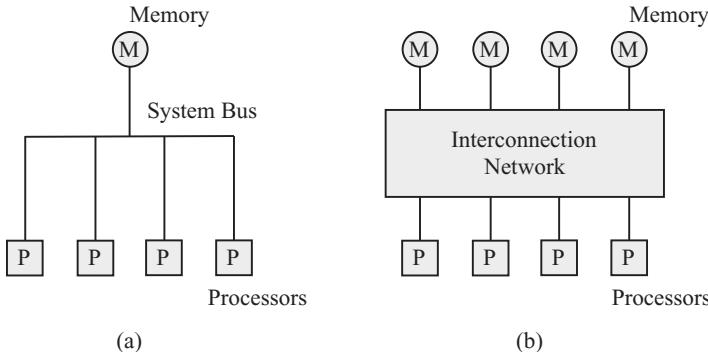

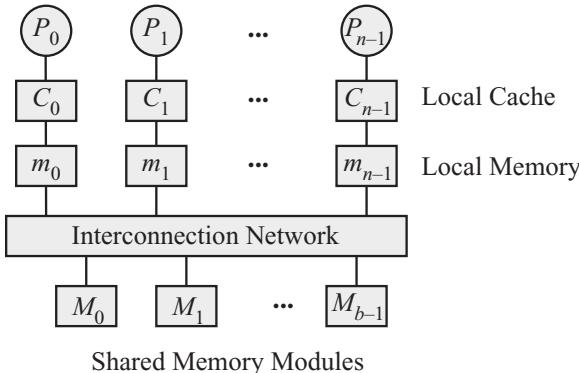

| 3.3 | Shared-Memory Multiprocessors (Uniform Memory Access [UMA])         | 54 |

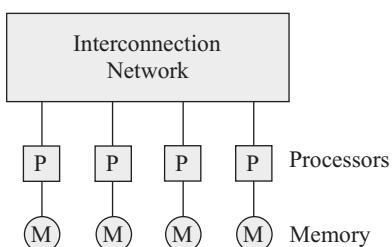

| 3.4 | Distributed-Memory Multiprocessor (Nonuniform Memory Access [NUMA]) | 56 |

---

|                                                    |                                                                  |            |

|----------------------------------------------------|------------------------------------------------------------------|------------|

| 3.5                                                | SIMD Processors                                                  | 57         |

| 3.6                                                | Systolic Processors                                              | 57         |

| 3.7                                                | Cluster Computing                                                | 60         |

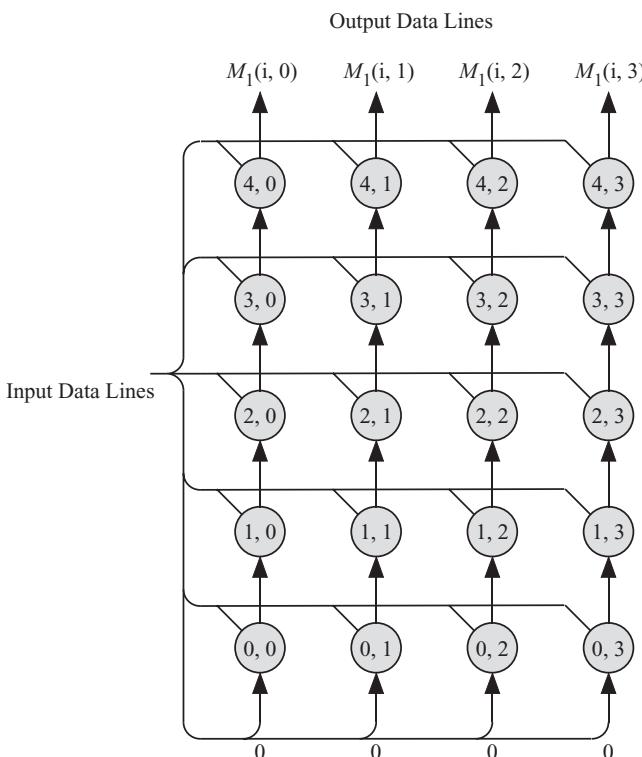

| 3.8                                                | Grid (Cloud) Computing                                           | 60         |

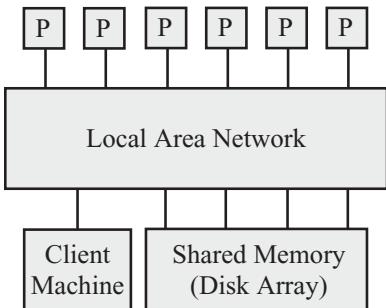

| 3.9                                                | Multicore Systems                                                | 61         |

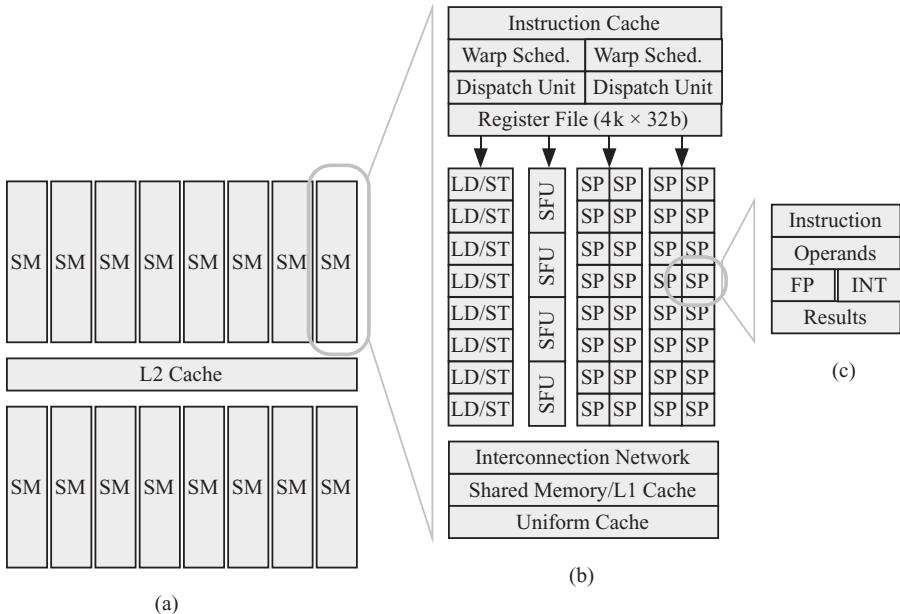

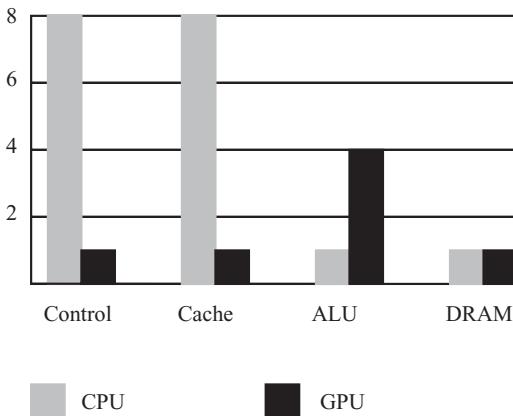

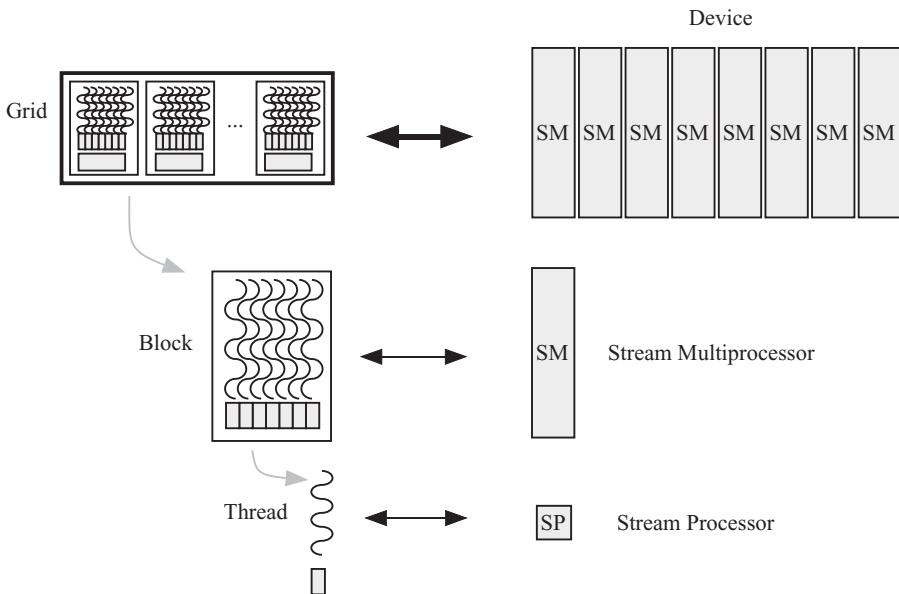

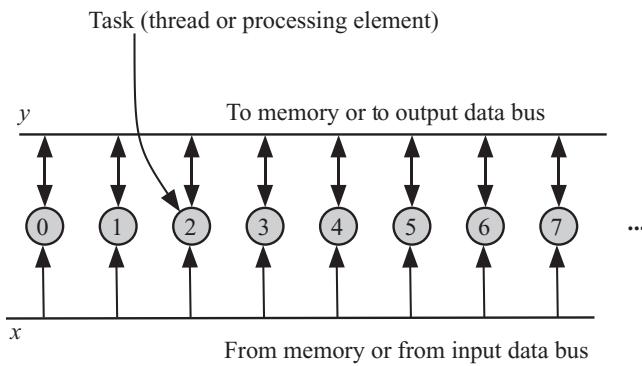

| 3.10                                               | SM                                                               | 62         |

| 3.11                                               | Communication Between Parallel Processors                        | 64         |

| 3.12                                               | Summary of Parallel Architectures                                | 67         |

| <b>4 Shared-Memory Multiprocessors</b>             |                                                                  | <b>69</b>  |

| 4.1                                                | Introduction                                                     | 69         |

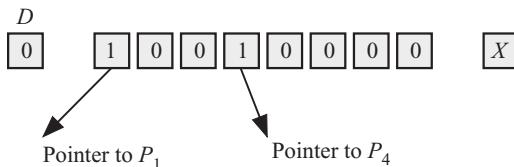

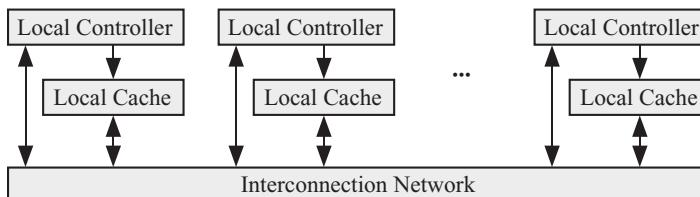

| 4.2                                                | Cache Coherence and Memory Consistency                           | 70         |

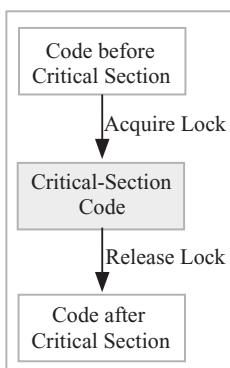

| 4.3                                                | Synchronization and Mutual Exclusion                             | 76         |

| <b>5 Interconnection Networks</b>                  |                                                                  | <b>83</b>  |

| 5.1                                                | Introduction                                                     | 83         |

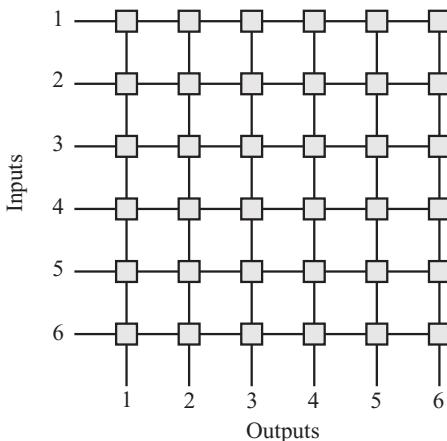

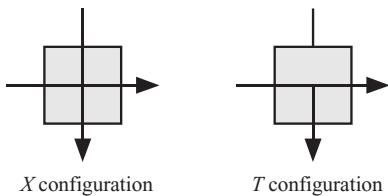

| 5.2                                                | Classification of Interconnection Networks by Logical Topologies | 84         |

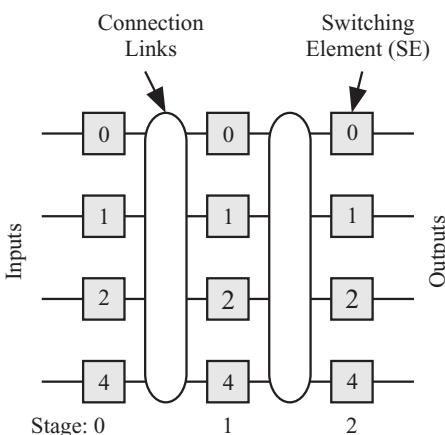

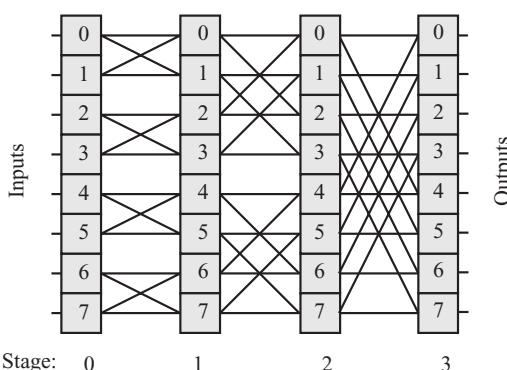

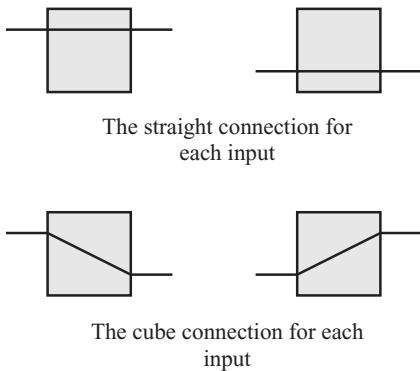

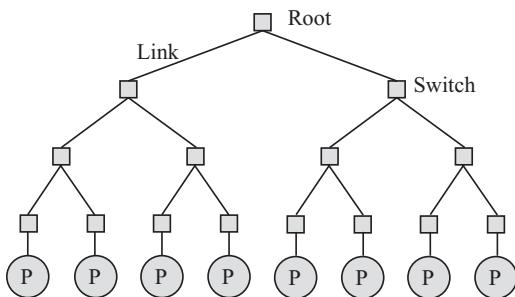

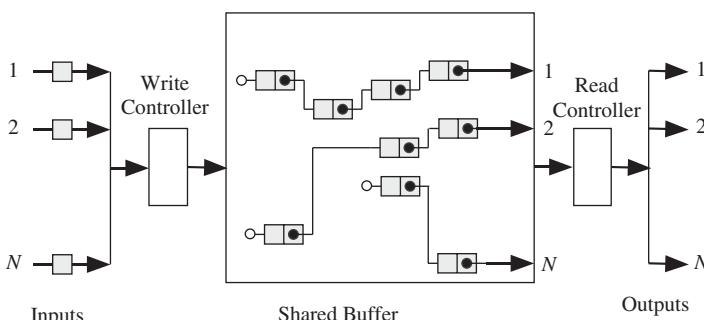

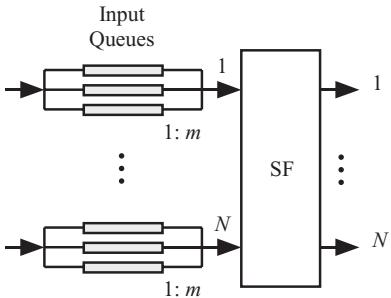

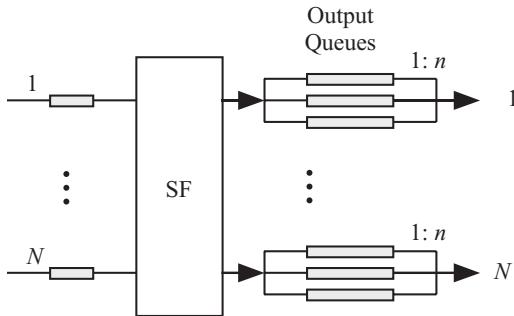

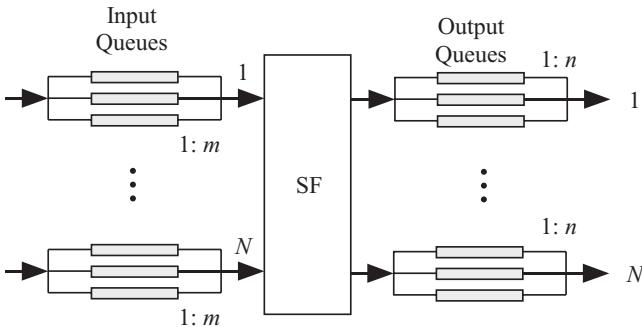

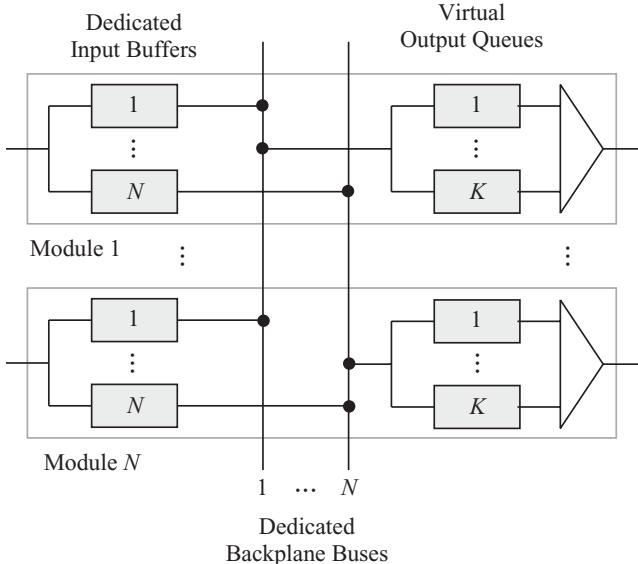

| 5.3                                                | Interconnection Network Switch Architecture                      | 91         |

| <b>6 Concurrency Platforms</b>                     |                                                                  | <b>105</b> |

| 6.1                                                | Introduction                                                     | 105        |

| 6.2                                                | Concurrency Platforms                                            | 105        |

| 6.3                                                | Cilk++                                                           | 106        |

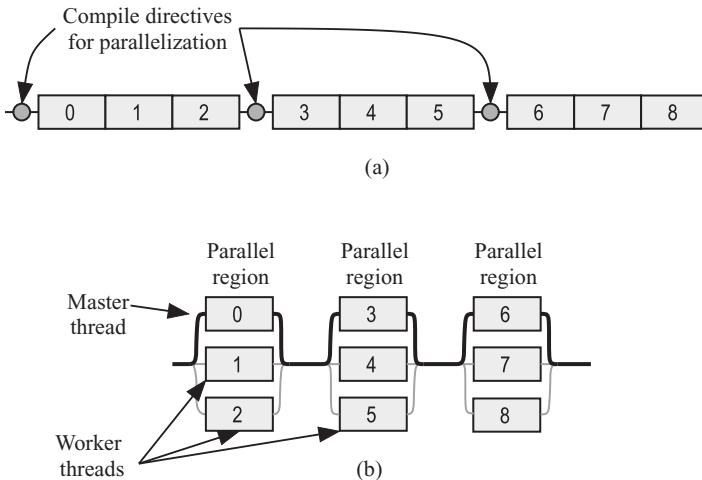

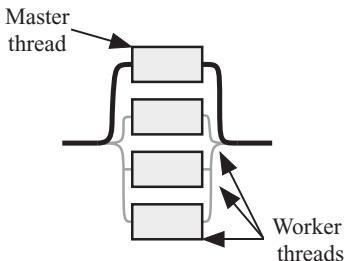

| 6.4                                                | OpenMP                                                           | 112        |

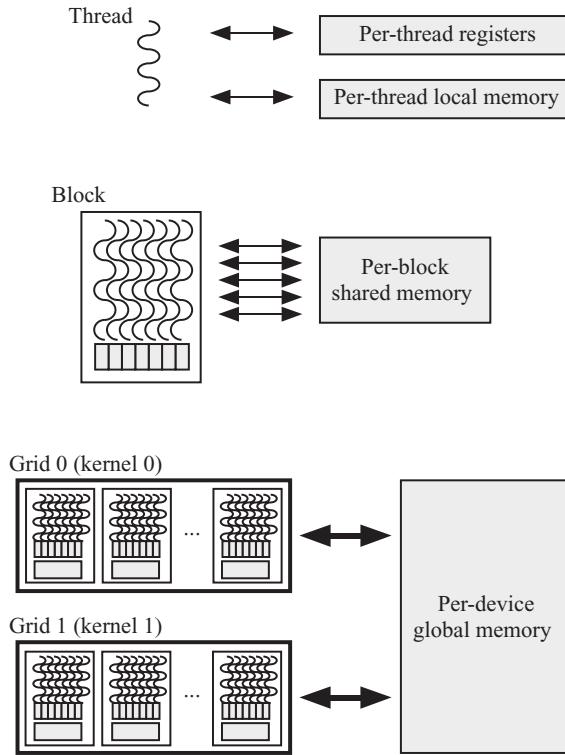

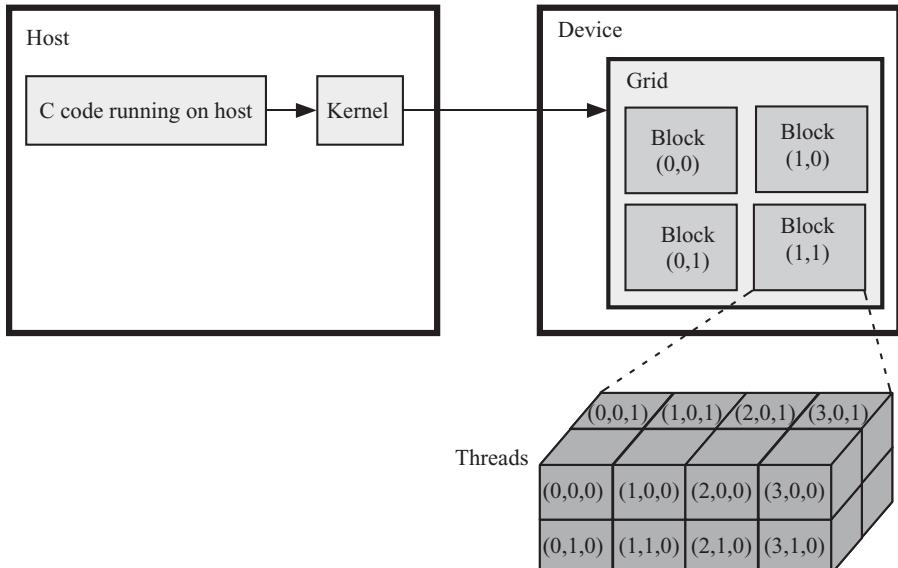

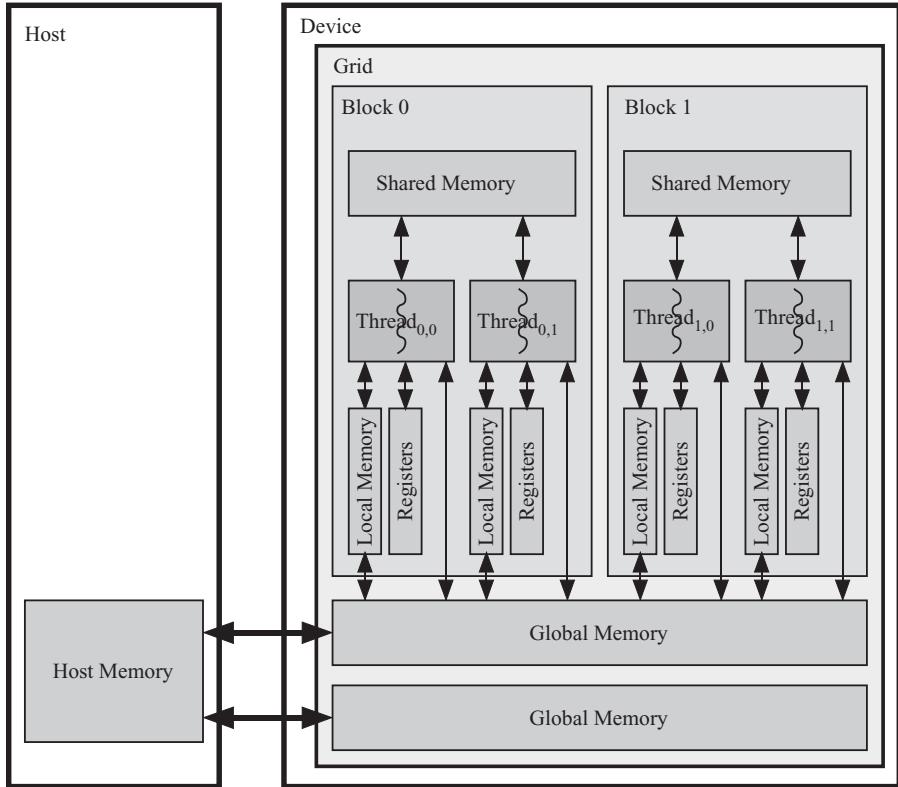

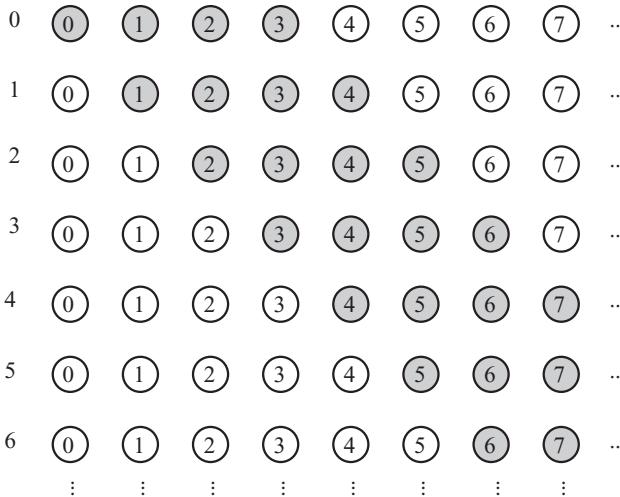

| 6.5                                                | Compute Unified Device Architecture (CUDA)                       | 122        |

| <b>7 Ad Hoc Techniques for Parallel Algorithms</b> |                                                                  | <b>131</b> |

| 7.1                                                | Introduction                                                     | 131        |

| 7.2                                                | Defining Algorithm Variables                                     | 133        |

| 7.3                                                | Independent Loop Scheduling                                      | 133        |

| 7.4                                                | Dependent Loops                                                  | 134        |

| 7.5                                                | Loop Spreading for Simple Dependent Loops                        | 135        |

| 7.6                                                | Loop Unrolling                                                   | 135        |

| 7.7                                                | Problem Partitioning                                             | 136        |

| 7.8                                                | Divide-and-Conquer (Recursive Partitioning) Strategies           | 137        |

| 7.9                                                | Pipelining                                                       | 139        |

| <b>8 Nonserial-Parallel Algorithms</b>             |                                                                  | <b>143</b> |

| 8.1                                                | Introduction                                                     | 143        |

| 8.2                                                | Comparing DAG and DCG Algorithms                                 | 143        |

| 8.3                                                | Parallelizing NSPA Algorithms Represented by a DAG               | 145        |

---

|     |                                                                        |     |

|-----|------------------------------------------------------------------------|-----|

| 8.4 | Formal Technique for Analyzing NSPAs                                   | 147 |

| 8.5 | Detecting Cycles in the Algorithm                                      | 150 |

| 8.6 | Extracting Serial and Parallel Algorithm Performance Parameters        | 151 |

| 8.7 | Useful Theorems                                                        | 153 |

| 8.8 | Performance of Serial and Parallel Algorithms<br>on Parallel Computers | 156 |

---

**9 *z*-Transform Analysis** **159**

|     |                                                                           |     |

|-----|---------------------------------------------------------------------------|-----|

| 9.1 | Introduction                                                              | 159 |

| 9.2 | Definition of <i>z</i> -Transform                                         | 159 |

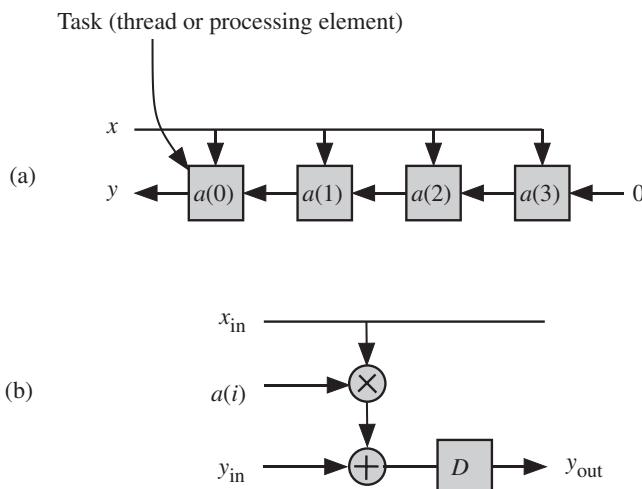

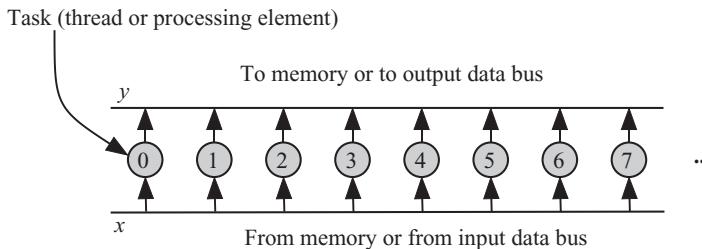

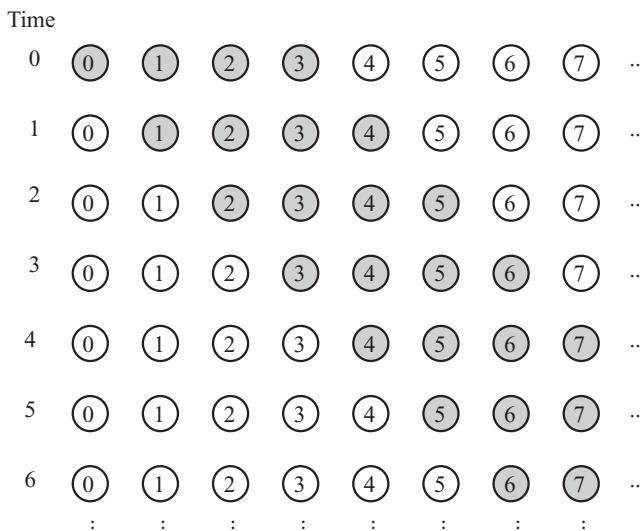

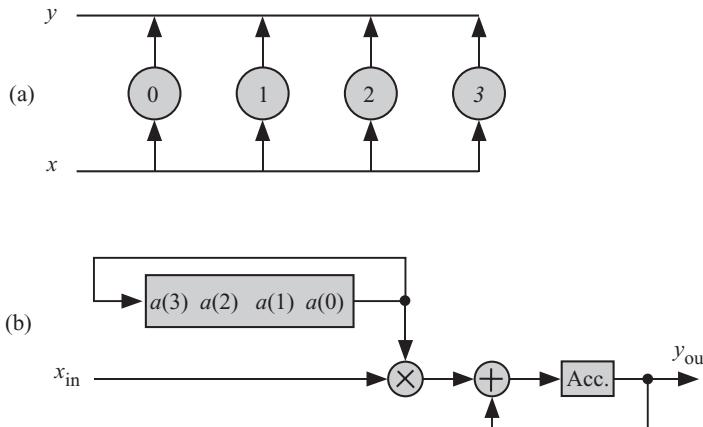

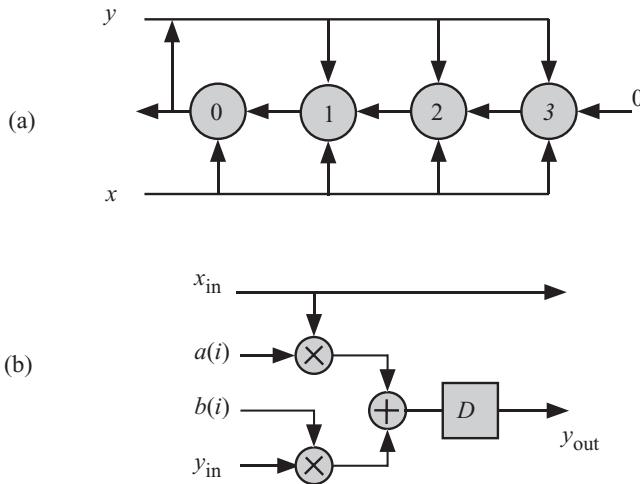

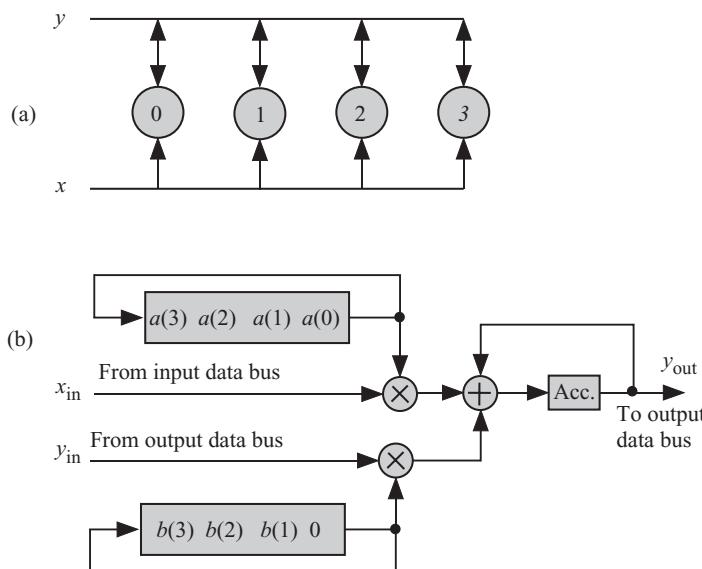

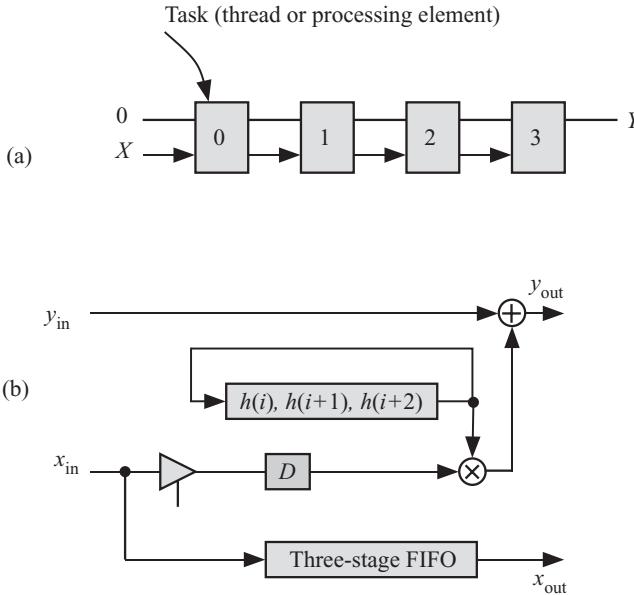

| 9.3 | The 1-D FIR Digital Filter Algorithm                                      | 160 |

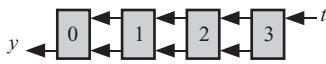

| 9.4 | Software and Hardware Implementations of the <i>z</i> -Transform          | 161 |

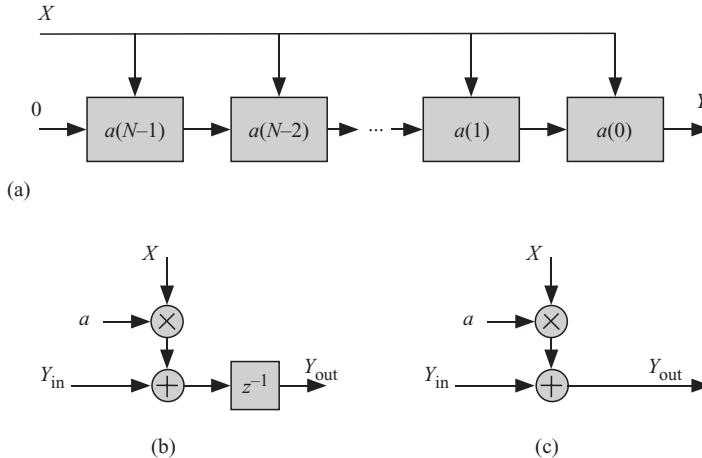

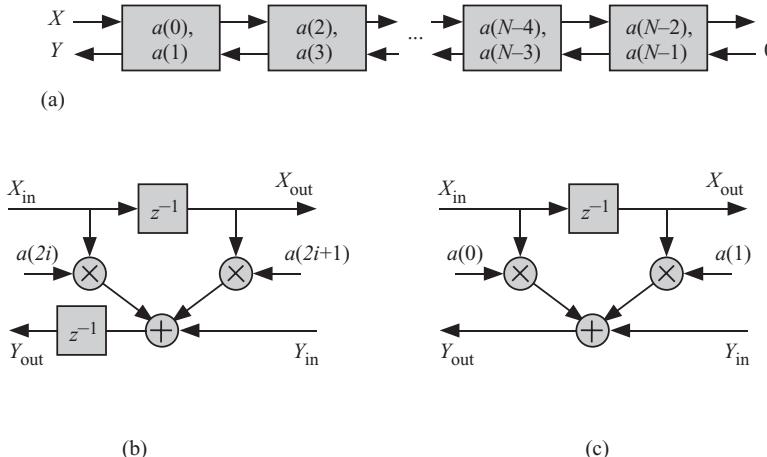

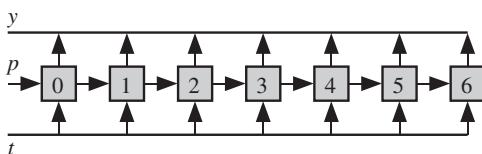

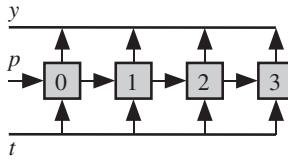

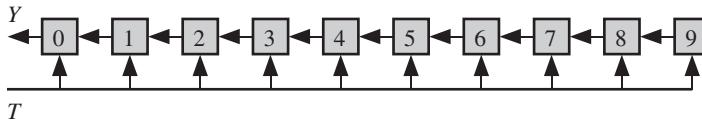

| 9.5 | Design 1: Using Horner's Rule for Broadcast Input and<br>Pipelined Output | 162 |

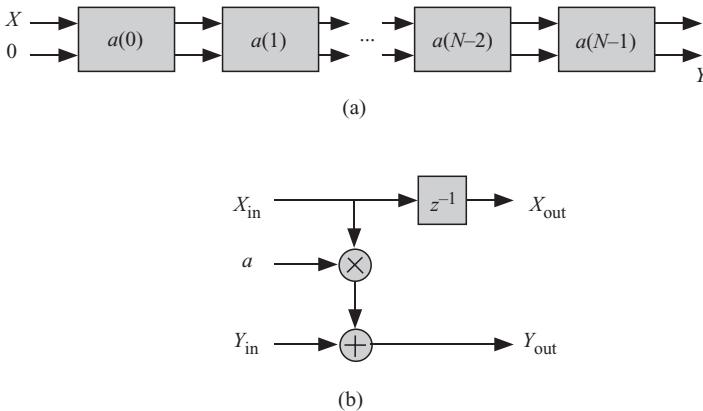

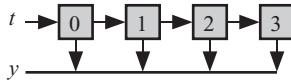

| 9.6 | Design 2: Pipelined Input and Broadcast Output                            | 163 |

| 9.7 | Design 3: Pipelined Input and Output                                      | 164 |

---

**10 Dependence Graph Analysis** **167**

|      |                                                            |     |

|------|------------------------------------------------------------|-----|

| 10.1 | Introduction                                               | 167 |

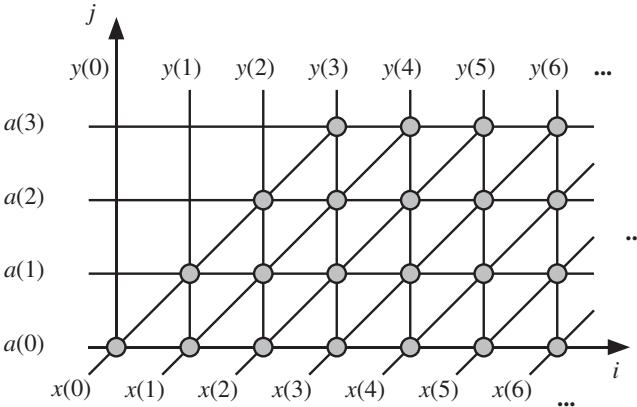

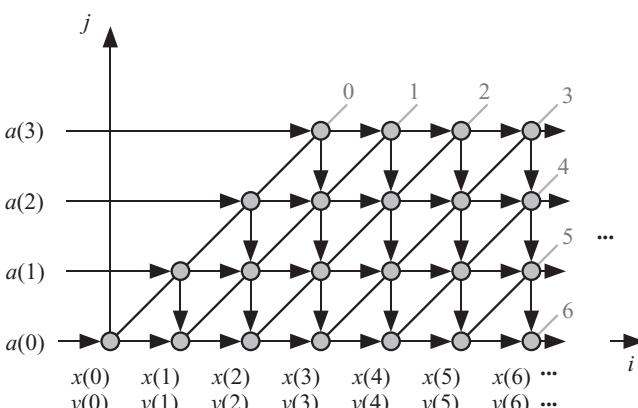

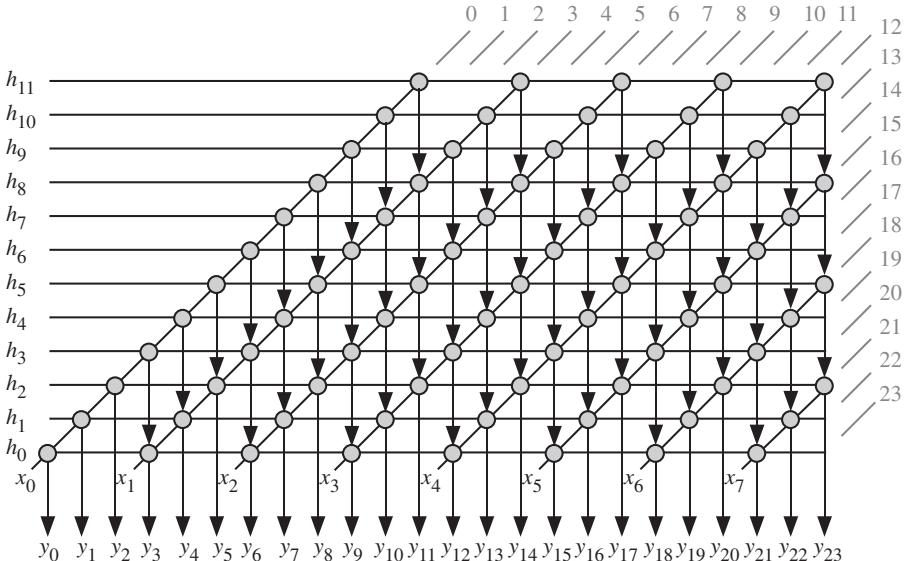

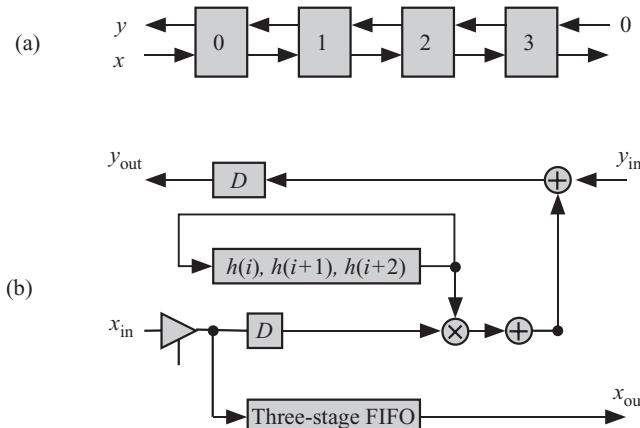

| 10.2 | The 1-D FIR Digital Filter Algorithm                       | 167 |

| 10.3 | The Dependence Graph of an Algorithm                       | 168 |

| 10.4 | Deriving the Dependence Graph for an Algorithm             | 169 |

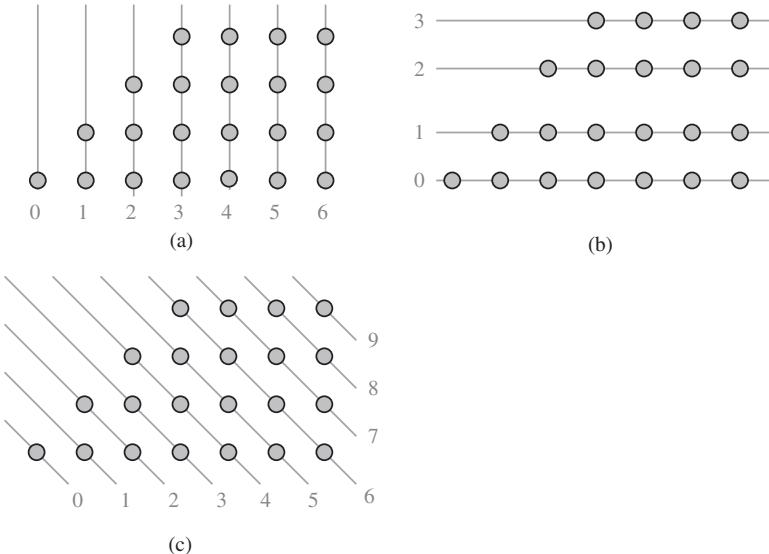

| 10.5 | The Scheduling Function for the 1-D FIR Filter             | 171 |

| 10.6 | Node Projection Operation                                  | 177 |

| 10.7 | Nonlinear Projection Operation                             | 179 |

| 10.8 | Software and Hardware Implementations of the DAG Technique | 180 |

---

**11 Computational Geometry Analysis** **185**

|       |                                                                                 |     |

|-------|---------------------------------------------------------------------------------|-----|

| 11.1  | Introduction                                                                    | 185 |

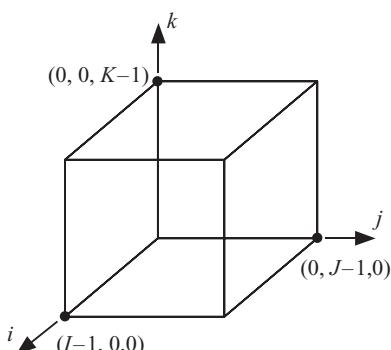

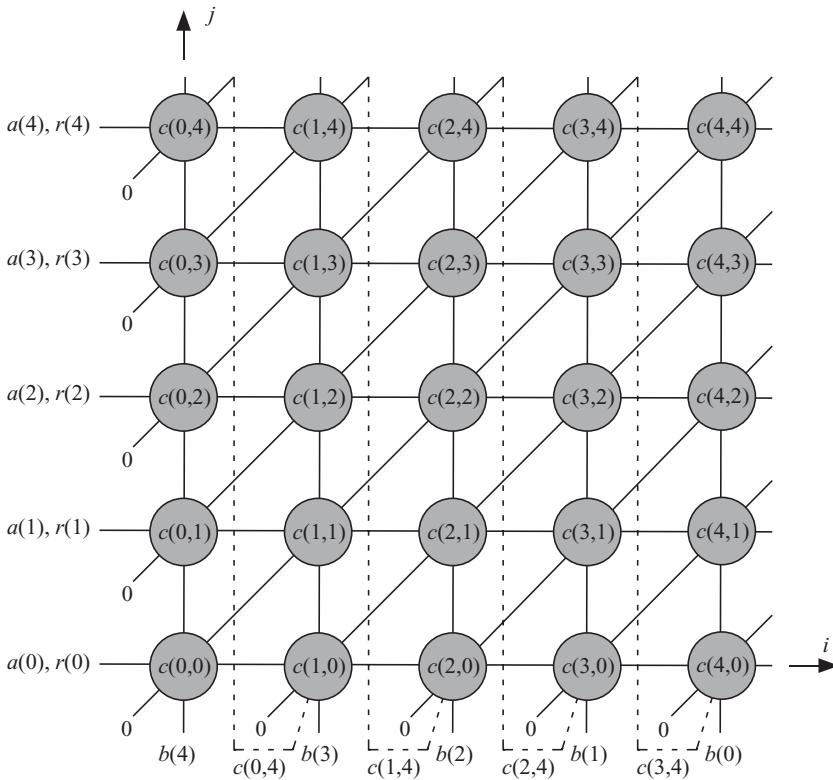

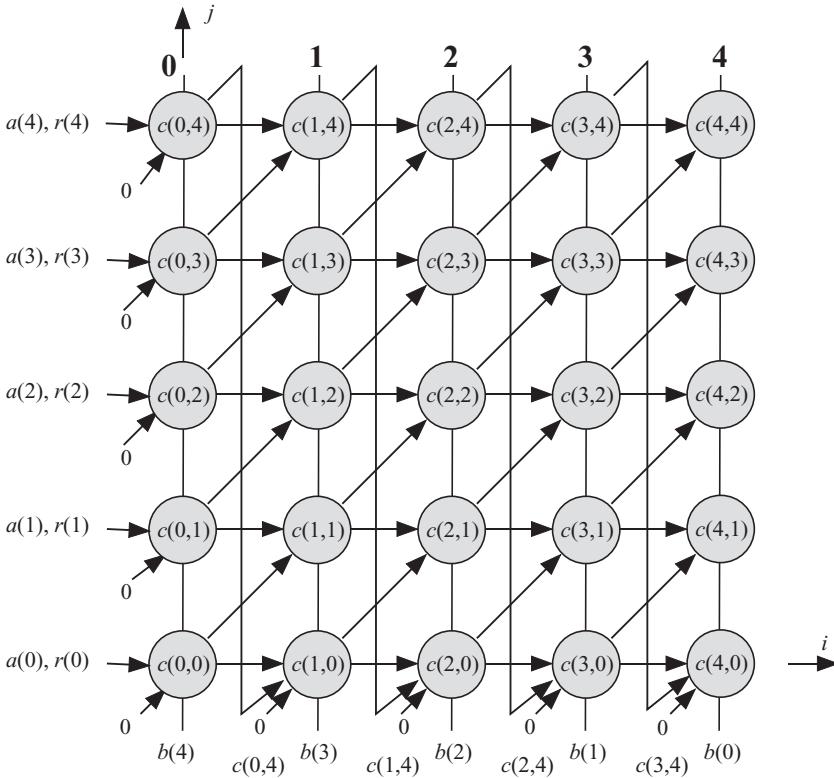

| 11.2  | Matrix Multiplication Algorithm                                                 | 185 |

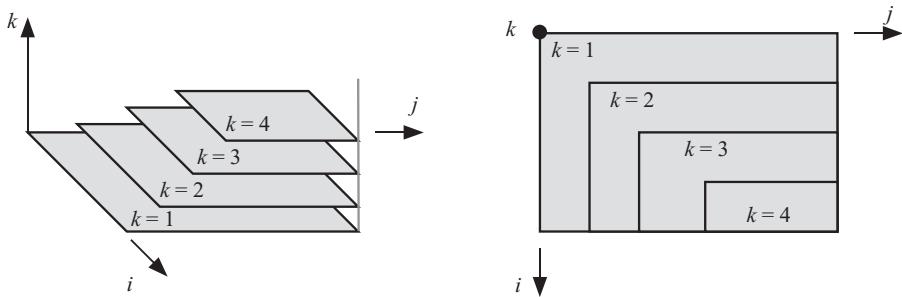

| 11.3  | The 3-D Dependence Graph and Computation Domain $\mathcal{D}$                   | 186 |

| 11.4  | The Facets and Vertices of $\mathcal{D}$                                        | 188 |

| 11.5  | The Dependence Matrices of the Algorithm Variables                              | 188 |

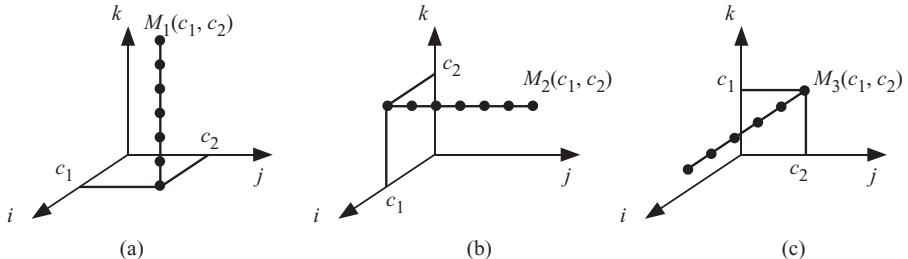

| 11.6  | Nullspace of Dependence Matrix: The Broadcast Subdomain $B$                     | 189 |

| 11.7  | Design Space Exploration: Choice of Broadcasting versus<br>Pipelining Variables | 192 |

| 11.8  | Data Scheduling                                                                 | 195 |

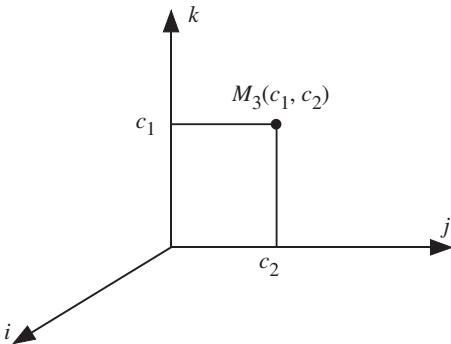

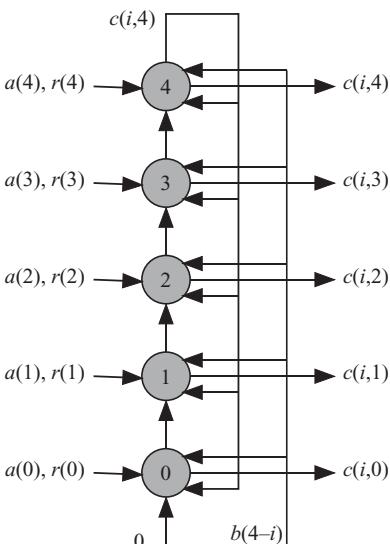

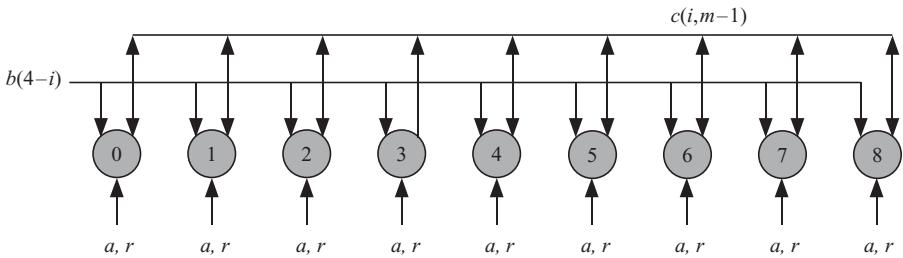

| 11.9  | Projection Operation Using the Linear Projection Operator                       | 200 |

| 11.10 | Effect of Projection Operation on Data                                          | 205 |

| 11.11 | The Resulting Multithreaded/Multiprocessor Architecture                         | 206 |

| 11.12 | Summary of Work Done in this Chapter                                            | 207 |

---

|                                                                      |            |

|----------------------------------------------------------------------|------------|

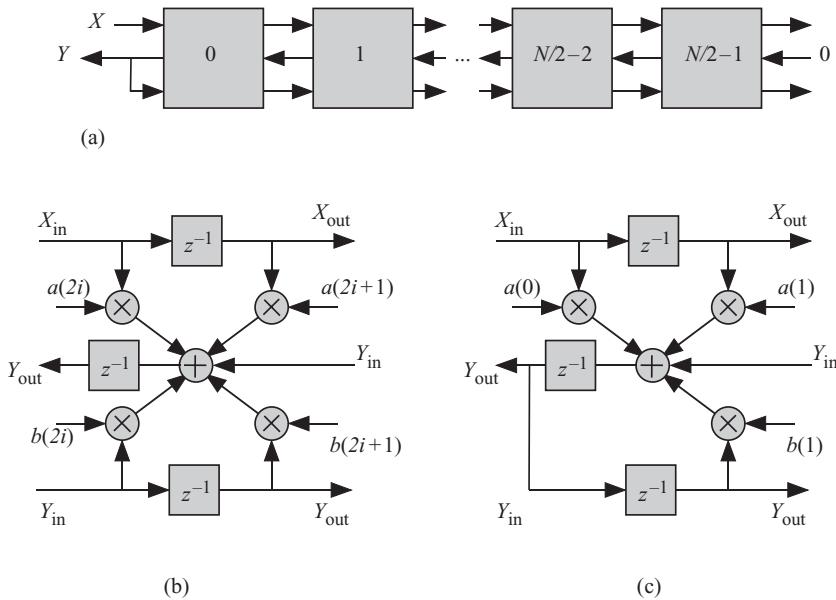

| <b>12 Case Study: One-Dimensional IIR Digital Filters</b>            | <b>209</b> |

| 12.1 Introduction                                                    | 209        |

| 12.2 The 1-D IIR Digital Filter Algorithm                            | 209        |

| 12.3 The IIR Filter Dependence Graph                                 | 209        |

| 12.4 z-Domain Analysis of 1-D IIR Digital Filter Algorithm           | 216        |

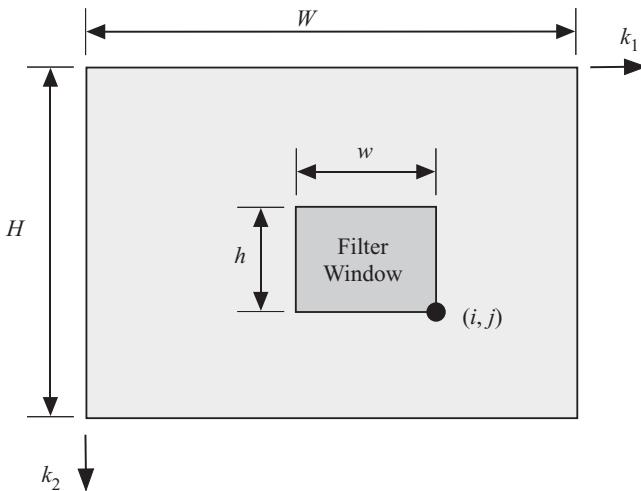

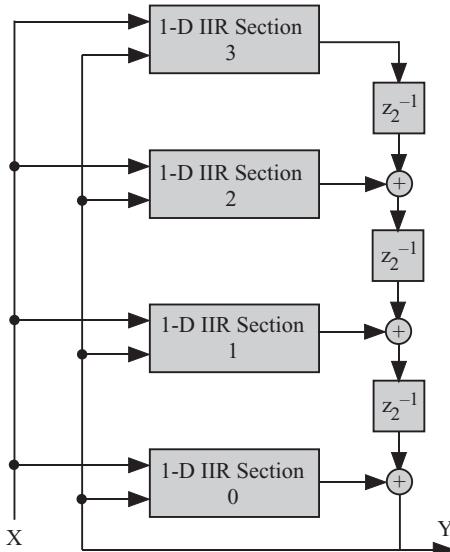

| <b>13 Case Study: Two- and Three-Dimensional Digital Filters</b>     | <b>219</b> |

| 13.1 Introduction                                                    | 219        |

| 13.2 Line and Frame Wraparound Problems                              | 219        |

| 13.3 2-D Recursive Filters                                           | 221        |

| 13.4 3-D Digital Filters                                             | 223        |

| <b>14 Case Study: Multirate Decimators and Interpolators</b>         | <b>227</b> |

| 14.1 Introduction                                                    | 227        |

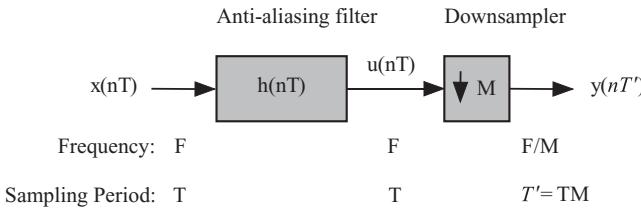

| 14.2 Decimator Structures                                            | 227        |

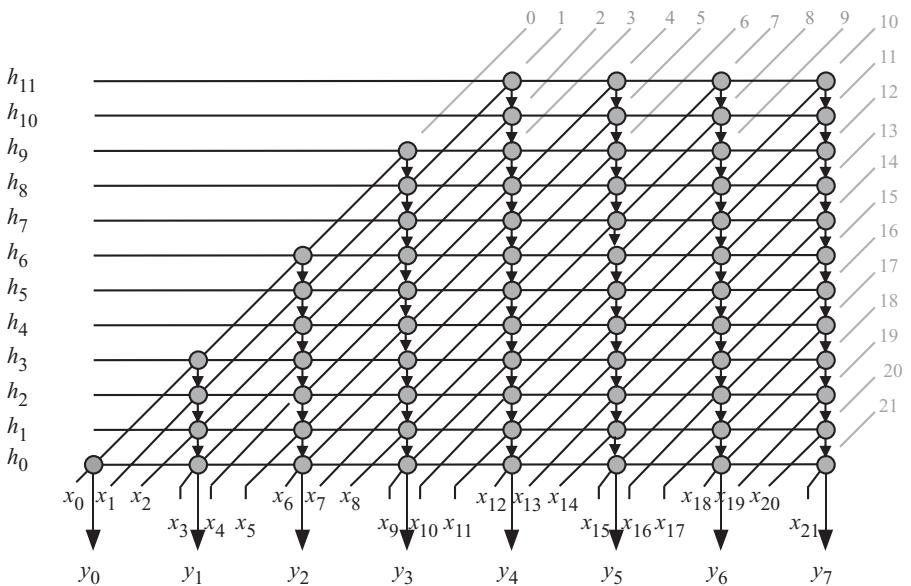

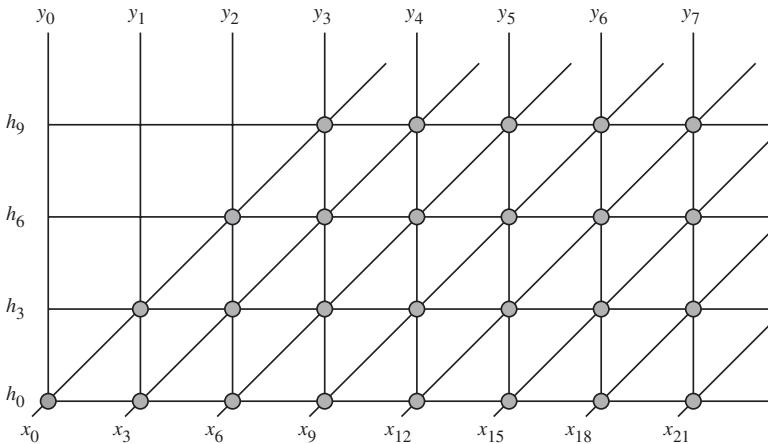

| 14.3 Decimator Dependence Graph                                      | 228        |

| 14.4 Decimator Scheduling                                            | 230        |

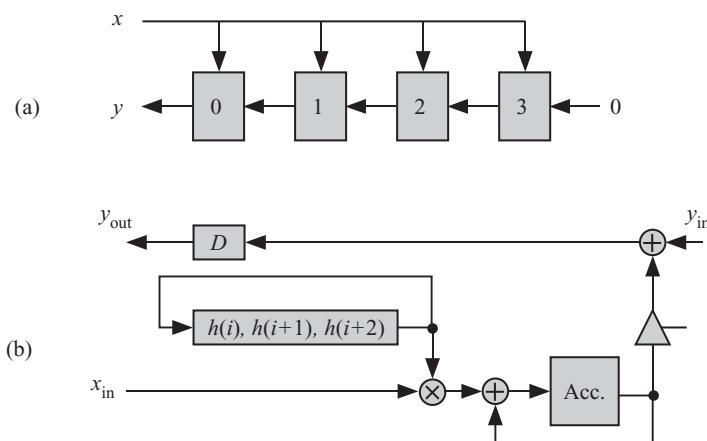

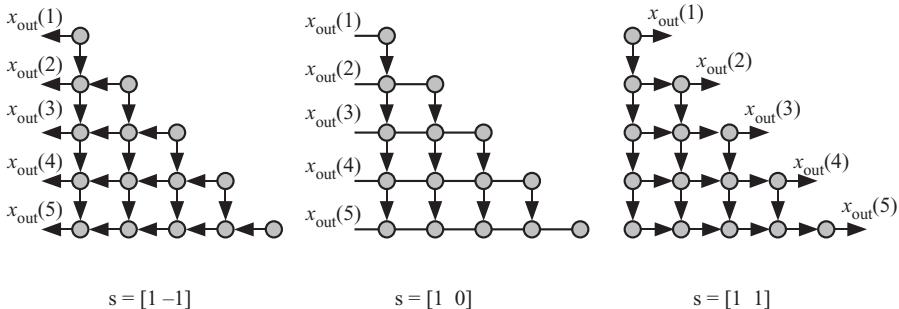

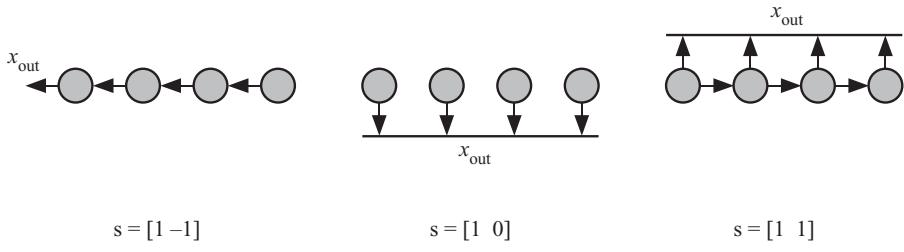

| 14.5 Decimator DAG for $s_1 = [1 0]$                                 | 231        |

| 14.6 Decimator DAG for $s_2 = [1 -1]$                                | 233        |

| 14.7 Decimator DAG for $s_3 = [1 1]$                                 | 235        |

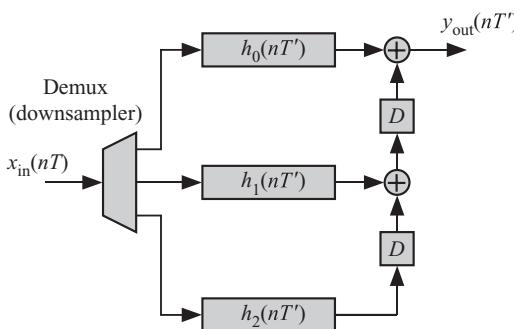

| 14.8 Polyphase Decimator Implementations                             | 235        |

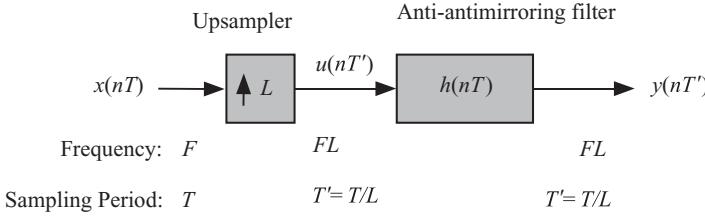

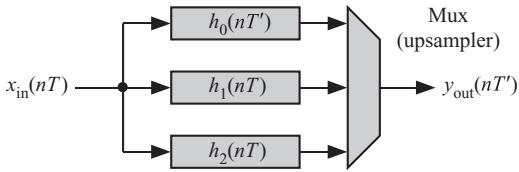

| 14.9 Interpolator Structures                                         | 236        |

| 14.10 Interpolator Dependence Graph                                  | 237        |

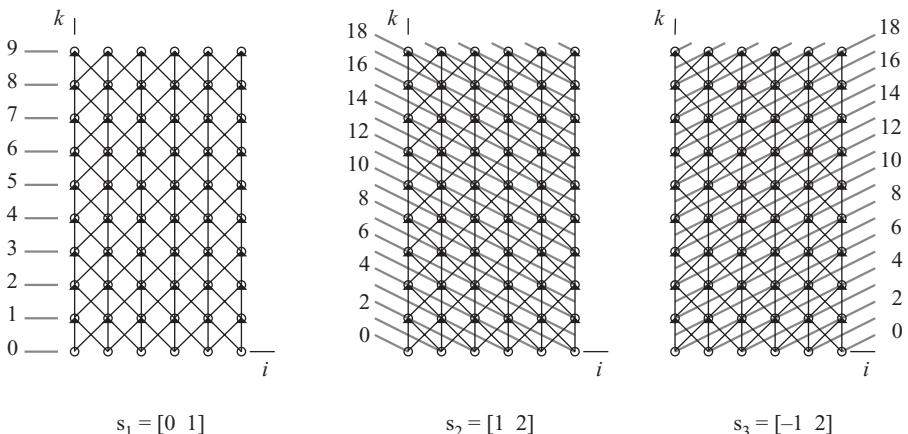

| 14.11 Interpolator Scheduling                                        | 238        |

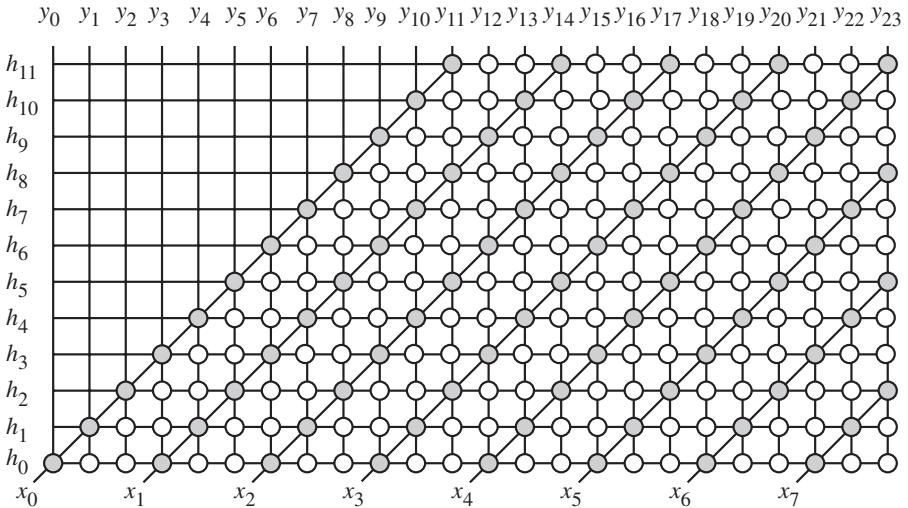

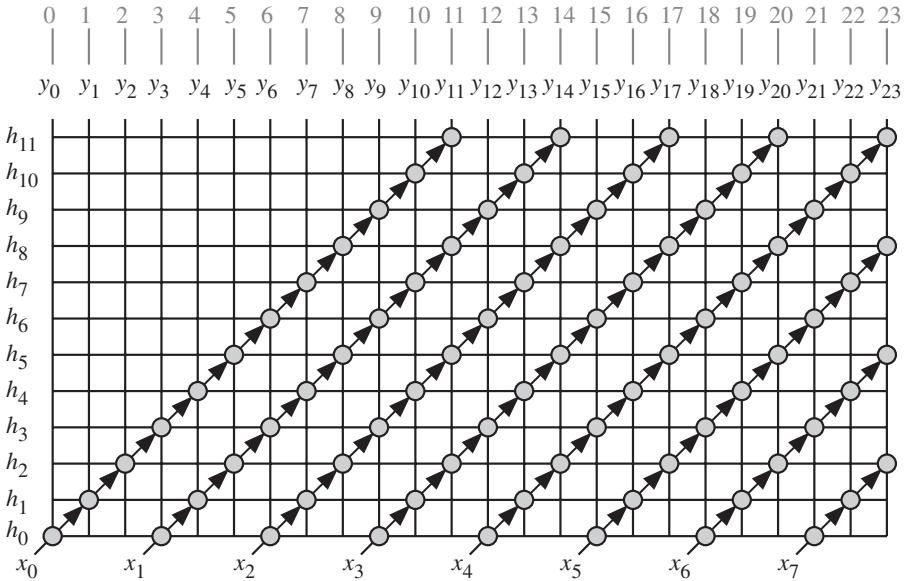

| 14.12 Interpolator DAG for $s_1 = [1 0]$                             | 239        |

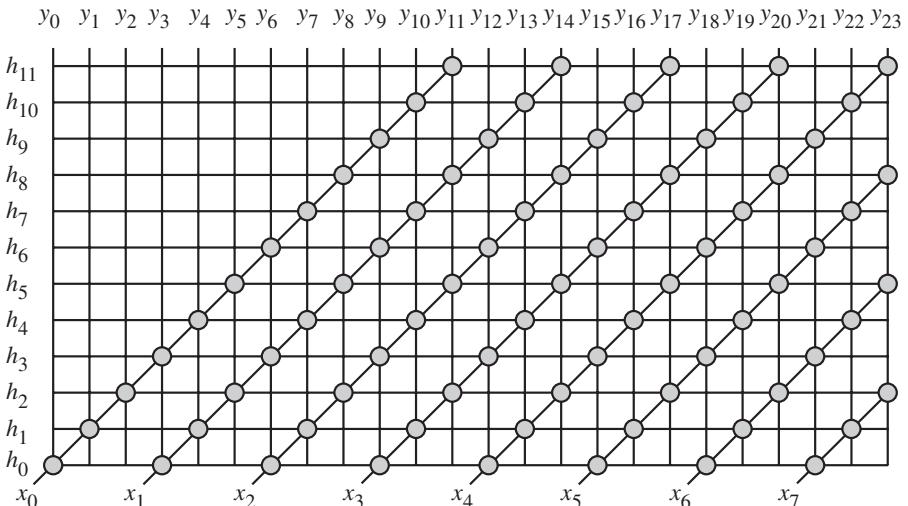

| 14.13 Interpolator DAG for $s_2 = [1 -1]$                            | 241        |

| 14.14 Interpolator DAG for $s_3 = [1 1]$                             | 243        |

| 14.15 Polyphase Interpolator Implementations                         | 243        |

| <b>15 Case Study: Pattern Matching</b>                               | <b>245</b> |

| 15.1 Introduction                                                    | 245        |

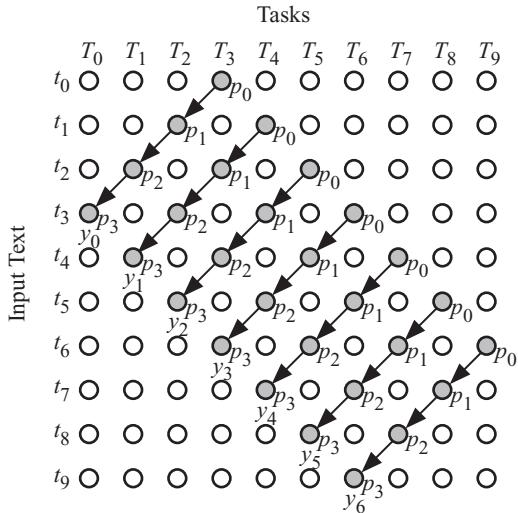

| 15.2 Expressing the Algorithm as a Regular Iterative Algorithm (RIA) | 245        |

| 15.3 Obtaining the Algorithm Dependence Graph                        | 246        |

| 15.4 Data Scheduling                                                 | 247        |

| 15.5 DAG Node Projection                                             | 248        |

| 15.6 DESIGN 1: Design Space Exploration When $s = [1 1]'$            | 249        |

| 15.7 DESIGN 2: Design Space Exploration When $s = [1 -1]'$           | 252        |

| 15.8 DESIGN 3: Design Space Exploration When $s = [1 0]'$            | 253        |

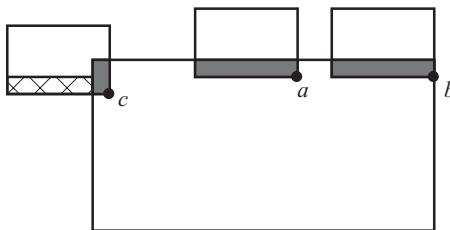

| <b>16 Case Study: Motion Estimation for Video Compression</b>        | <b>255</b> |

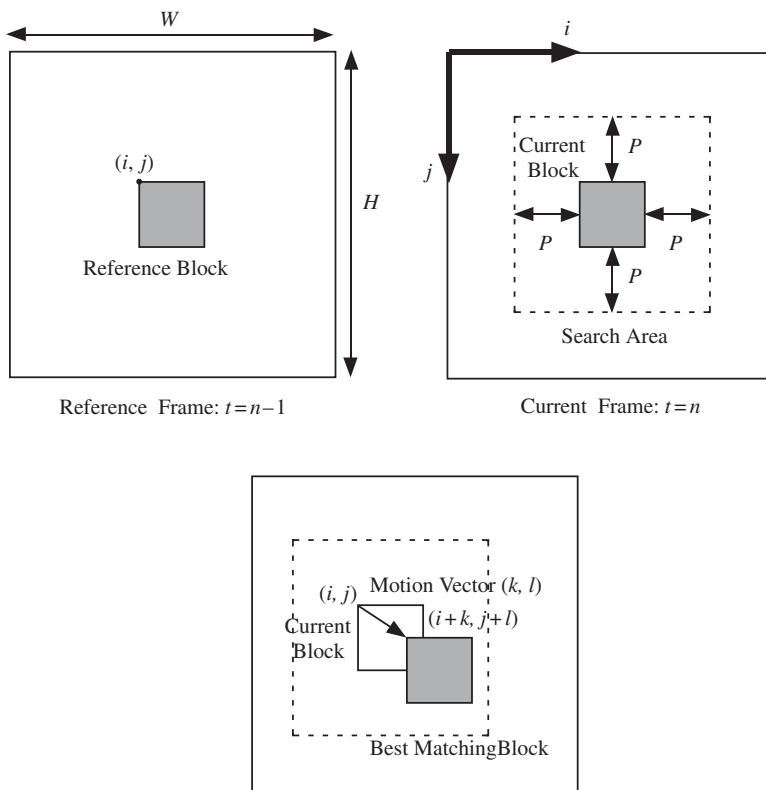

| 16.1 Introduction                                                    | 255        |

| 16.2 FBMAs                                                           | 256        |

---

---

|      |                                               |     |

|------|-----------------------------------------------|-----|

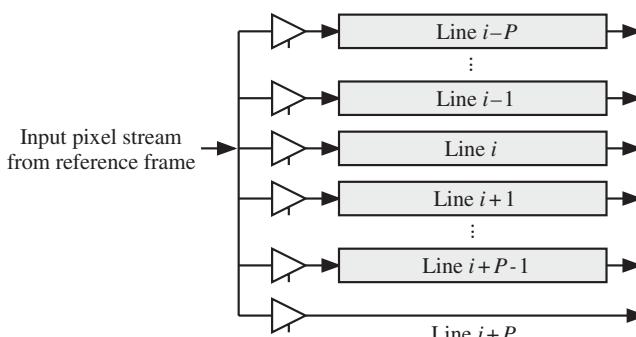

| 16.3 | Data Buffering Requirements                   | 257 |

| 16.4 | Formulation of the FBMA                       | 258 |

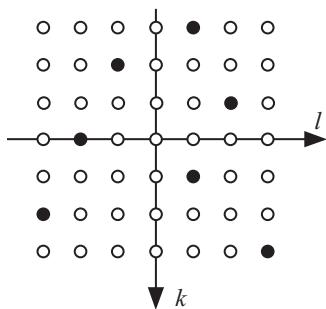

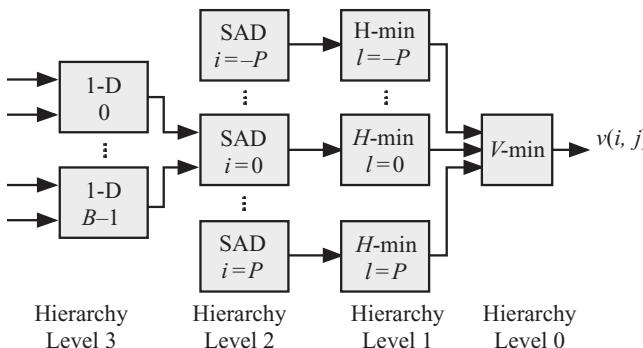

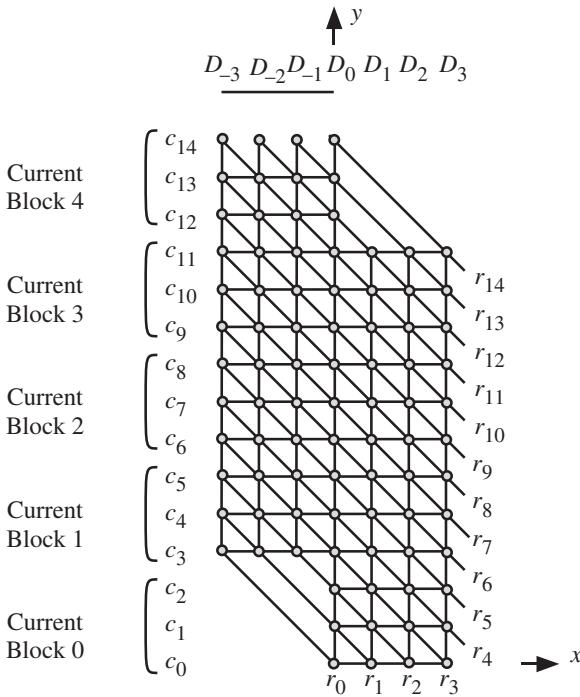

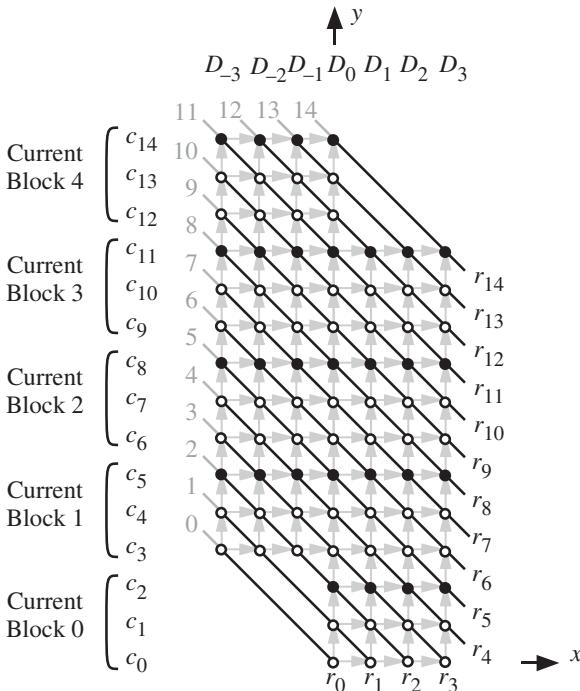

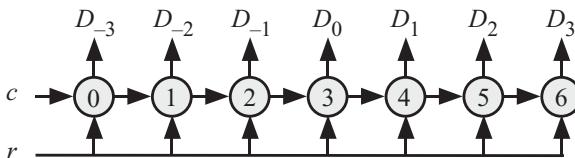

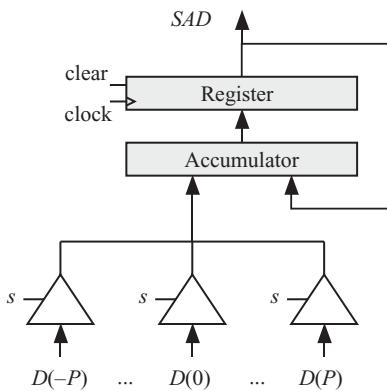

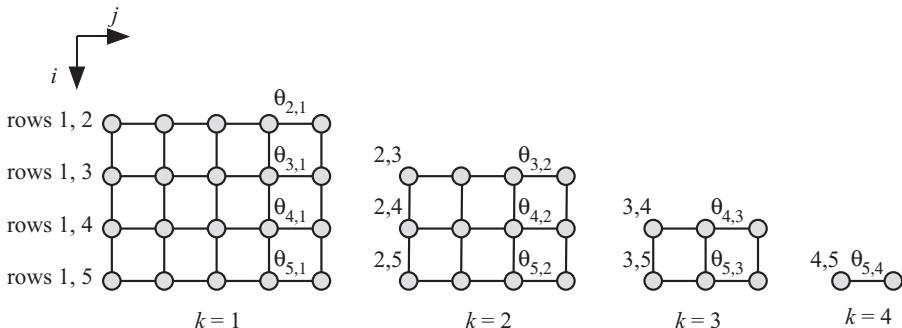

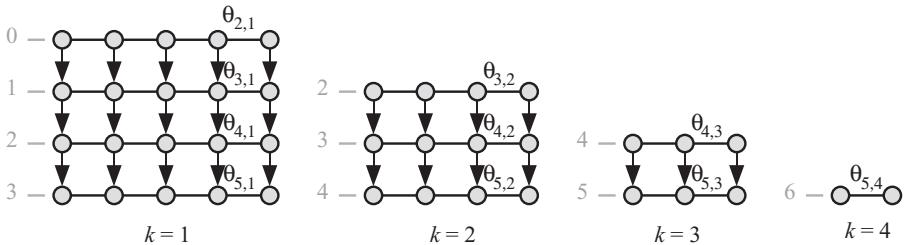

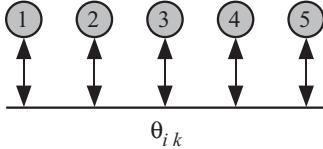

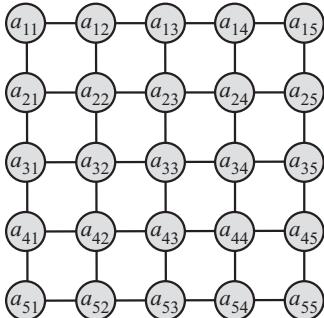

| 16.5 | Hierarchical Formulation of Motion Estimation | 259 |

| 16.6 | Hardware Design of the Hierarchy Blocks       | 261 |

**17 Case Study: Multiplication over GF( $2^m$ )** **267**

---

|       |                                             |     |

|-------|---------------------------------------------|-----|

| 17.1  | Introduction                                | 267 |

| 17.2  | The Multiplication Algorithm in GF( $2^m$ ) | 268 |

| 17.3  | Expressing Field Multiplication as an RIA   | 270 |

| 17.4  | Field Multiplication Dependence Graph       | 270 |

| 17.5  | Data Scheduling                             | 271 |

| 17.6  | DAG Node Projection                         | 273 |

| 17.7  | Design 1: Using $d_1 = [1 \ 0]^t$           | 275 |

| 17.8  | Design 2: Using $d_2 = [1 \ 1]^t$           | 275 |

| 17.9  | Design 3: Using $d_3 = [1 \ -1]^t$          | 277 |

| 17.10 | Applications of Finite Field Multipliers    | 277 |

**18 Case Study: Polynomial Division over GF(2)** **279**

---

|      |                                                            |     |

|------|------------------------------------------------------------|-----|

| 18.1 | Introduction                                               | 279 |

| 18.2 | The Polynomial Division Algorithm                          | 279 |

| 18.3 | The LFSR Dependence Graph                                  | 281 |

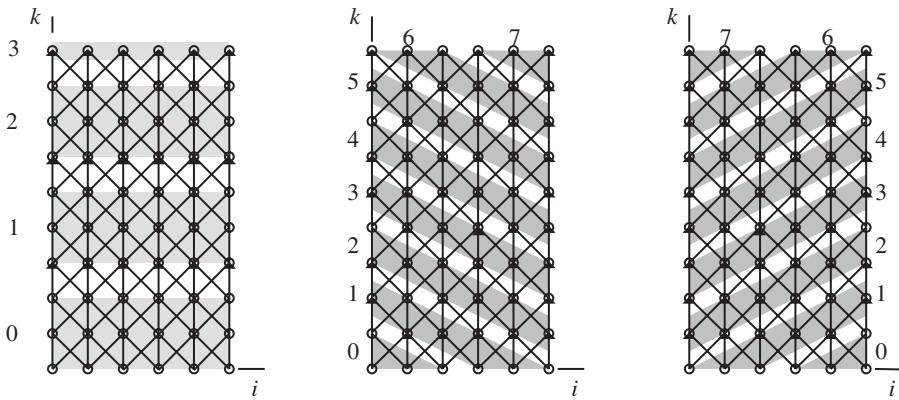

| 18.4 | Data Scheduling                                            | 282 |

| 18.5 | DAG Node Projection                                        | 283 |

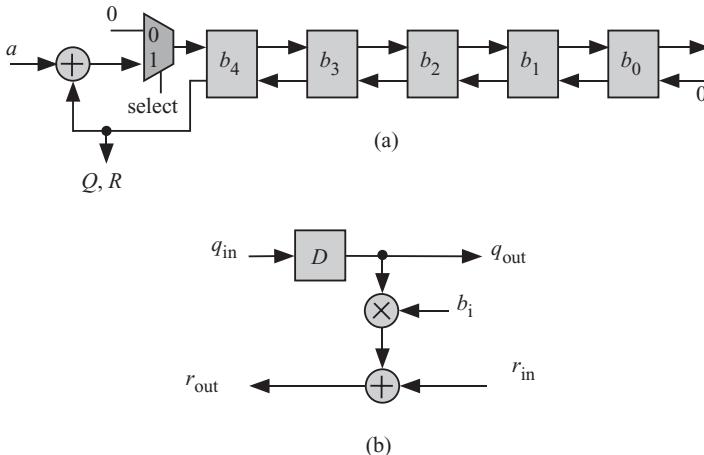

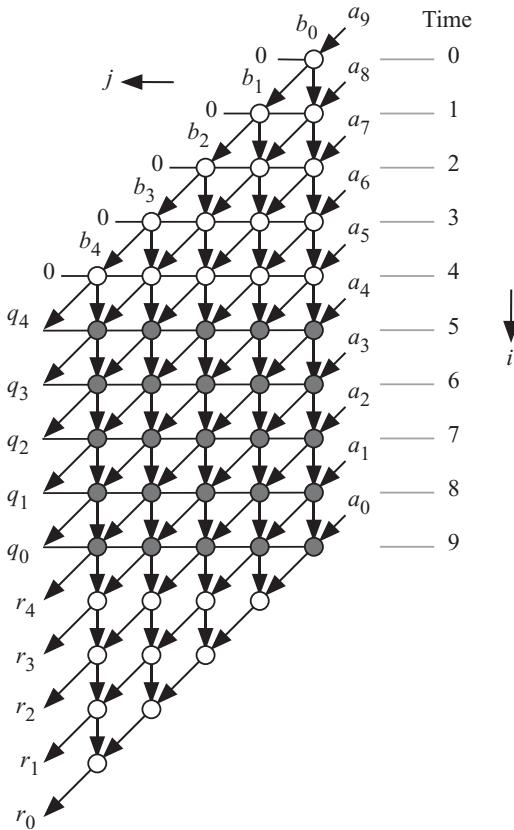

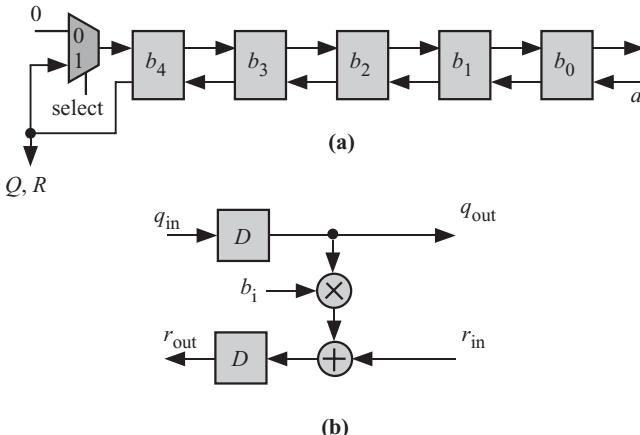

| 18.6 | Design 1: Design Space Exploration When $s_1 = [1 \ -1]$   | 284 |

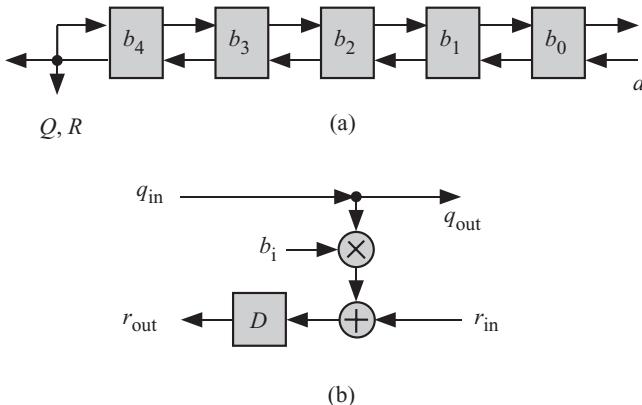

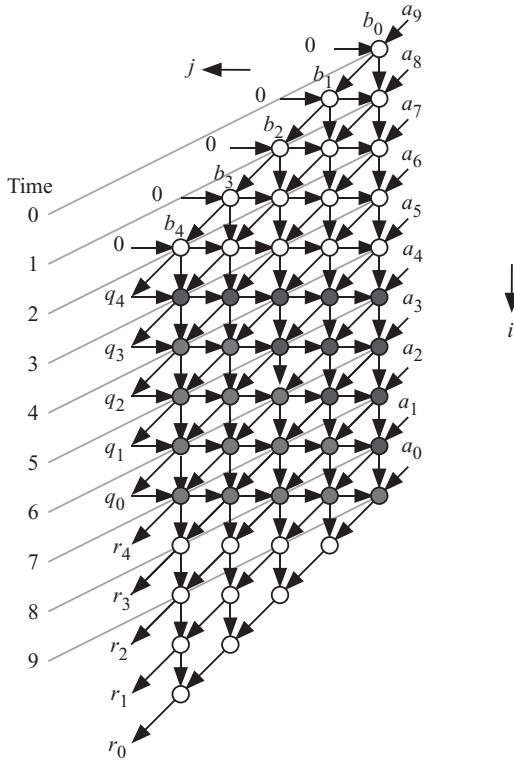

| 18.7 | Design 2: Design Space Exploration When $s_2 = [1 \ 0]$    | 286 |

| 18.8 | Design 3: Design Space Exploration When $s_3 = [1 \ -0.5]$ | 289 |

| 18.9 | Comparing the Three Designs                                | 291 |

**19 The Fast Fourier Transform** **293**

---

|      |                                                        |     |

|------|--------------------------------------------------------|-----|

| 19.1 | Introduction                                           | 293 |

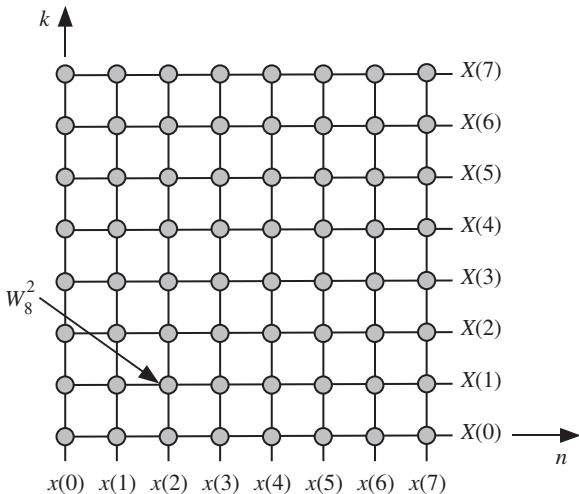

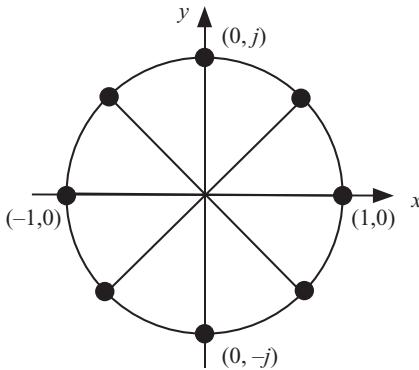

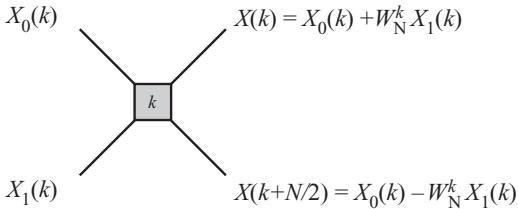

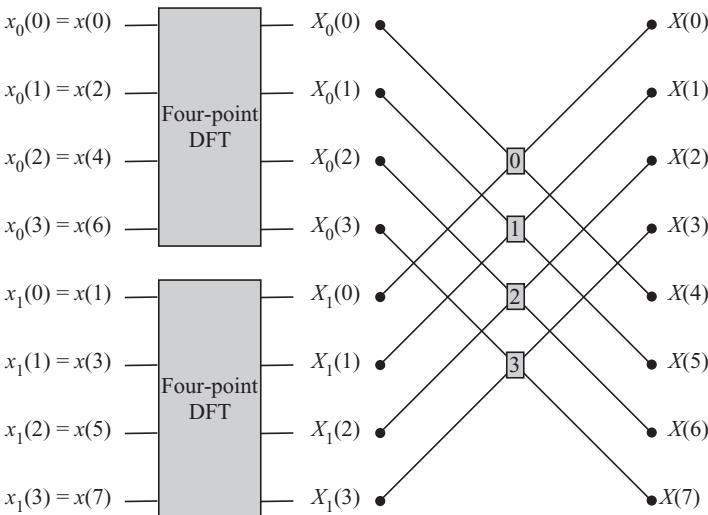

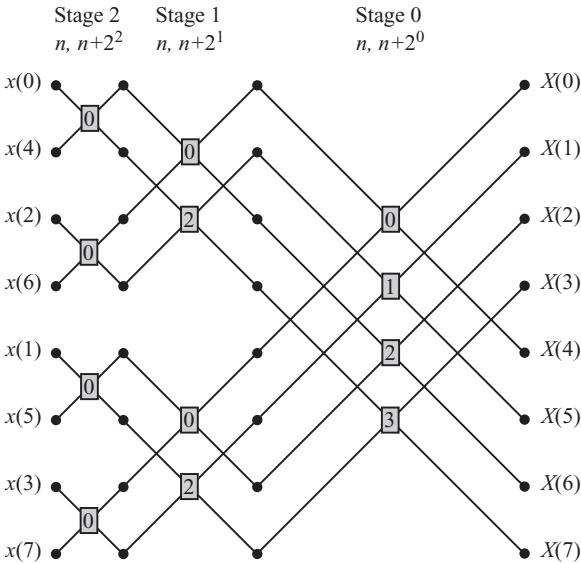

| 19.2 | Decimation-in-Time FFT                                 | 295 |

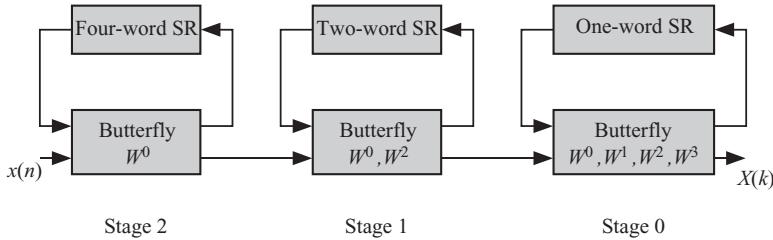

| 19.3 | Pipeline Radix-2 Decimation-in-Time FFT Processor      | 298 |

| 19.4 | Decimation-in-Frequency FFT                            | 299 |

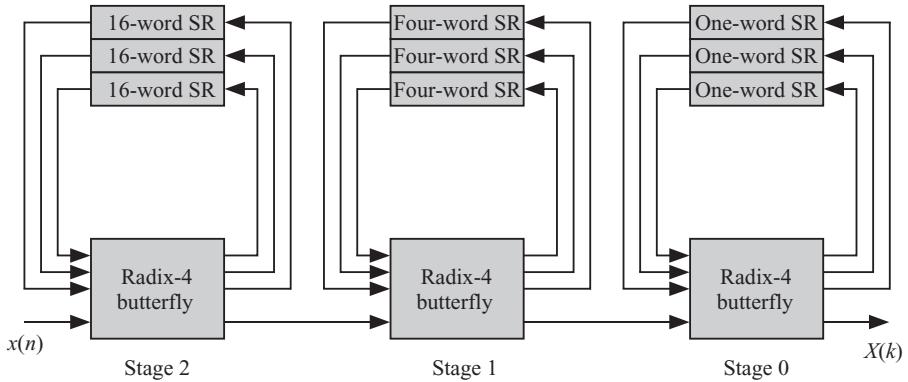

| 19.5 | Pipeline Radix-2 Decimation-in-Frequency FFT Processor | 303 |

**20 Solving Systems of Linear Equations** **305**

---

|      |                                                        |     |

|------|--------------------------------------------------------|-----|

| 20.1 | Introduction                                           | 305 |

| 20.2 | Special Matrix Structures                              | 305 |

| 20.3 | Forward Substitution (Direct Technique)                | 309 |

| 20.4 | Back Substitution                                      | 312 |

| 20.5 | Matrix Triangularization Algorithm                     | 312 |

| 20.6 | Successive over Relaxation (SOR) (Iterative Technique) | 317 |

| 20.7 | Problems                                               | 321 |

---

|                   |                                                                              |            |

|-------------------|------------------------------------------------------------------------------|------------|

| <b>21</b>         | <b>Solving Partial Differential Equations Using Finite Difference Method</b> | <b>323</b> |

| 21.1              | Introduction                                                                 | 323        |

| 21.2              | FDM for 1-D Systems                                                          | 324        |

| <b>References</b> |                                                                              | <b>331</b> |

| <b>Index</b>      |                                                                              | <b>337</b> |

# Preface

---

## ABOUT THIS BOOK

There is a *software gap* between hardware potential and the performance that can be attained using today's software parallel program development tools. The tools need manual intervention by the programmer to parallelize the code. This book is intended to give the programmer the techniques necessary to explore parallelism in algorithms, serial as well as iterative. Parallel computing is now moving from the realm of specialized expensive systems available to few select groups to cover almost every computing system in use today. We can find parallel computers in our laptops, desktops, and embedded in our smart phones. The applications and algorithms targeted to parallel computers were traditionally confined to weather prediction, wind tunnel simulations, computational biology, and signal processing. Nowadays, just about any application that runs on a computer will encounter the parallel processors now available in almost every system.

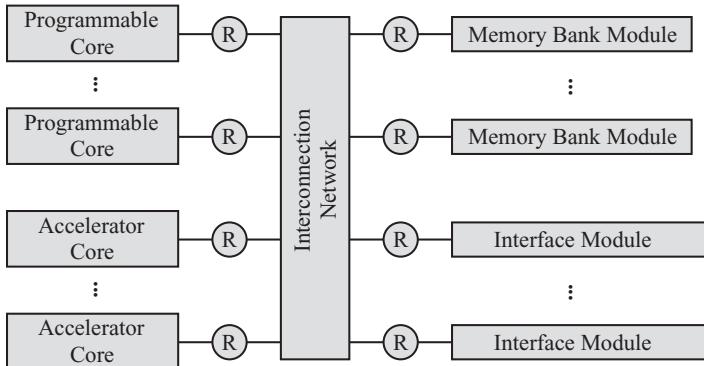

Parallel algorithms could now be designed to run on special-purpose parallel processors or could run on general-purpose parallel processors using several multi-level techniques such as parallel program development, parallelizing compilers, multithreaded operating systems, and superscalar processors. This book covers the first option: design of special-purpose parallel processor architectures to implement a given class of algorithms. We call such systems accelerator cores. This book forms the basis for a course on design and analysis of parallel algorithms. The course would cover Chapters 1–4 then would select several of the case study chapters that constitute the remainder of the book.

Although very large-scale integration (VLSI) technology allows us to integrate more processors on the same chip, parallel programming is not advancing to match these technological advances. An obvious application of parallel hardware is to design special-purpose parallel processors primarily intended for use as accelerator cores in multicore systems. This is motivated by two practicalities: the prevalence of multicore systems in current computing platforms and the abundance of simple parallel algorithms that are needed in many systems, such as in data encryption/decryption, graphics processing, digital signal processing and filtering, and many more.

It is simpler to start by stating what this book is *not* about. This book does not attempt to give a detailed coverage of computer architecture, parallel computers, or algorithms in general. Each of these three topics deserves a large textbook to attempt to provide a good cover. Further, there are the standard and excellent textbooks for each, such as *Computer Organization and Design* by D.A. Patterson and J.L.

Hennessy, *Parallel Computer Architecture* by D.E. Culler, J.P. Singh, and A. Gupta, and finally, *Introduction to Algorithms* by T.H. Cormen, C.E. Leiserson, and R.L. Rivest. I hope many were fortunate enough to study these topics in courses that adopted the above textbooks. My apologies if I did not include a comprehensive list of equally good textbooks on the above subjects.

This book, on the other hand, shows how to systematically design special-purpose parallel processing structures to implement algorithms. The techniques presented here are general and can be applied to many algorithms, parallel or otherwise.

This book is intended for researchers and graduate students in computer engineering, electrical engineering, and computer science. The prerequisites for this book are basic knowledge of linear algebra and digital signal processing. The objectives of this book are (1) to explain several techniques for expressing a parallel algorithm as a dependence graph or as a set of dependence matrices; (2) to explore scheduling schemes for the processing tasks while conforming to input and output data timing, and to be able to pipeline some data and broadcast other data to all processors; and (3) to explore allocation schemes for the processing tasks to processing elements.

## CHAPTER ORGANIZATION AND OVERVIEW

*Chapter 1* defines the two main classes of algorithms dealt with in this book: serial algorithms, parallel algorithms, and regular iterative algorithms. Design considerations for parallel computers are discussed as well as their close tie to parallel algorithms. The benefits of using parallel computers are quantified in terms of speedup factor and the effect of communication overhead between the processors. The chapter concludes by discussing two applications of parallel computers.

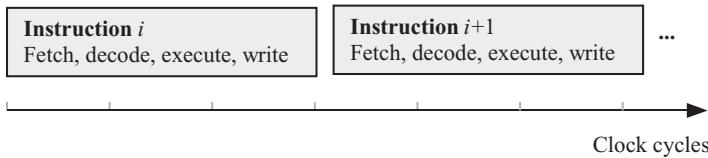

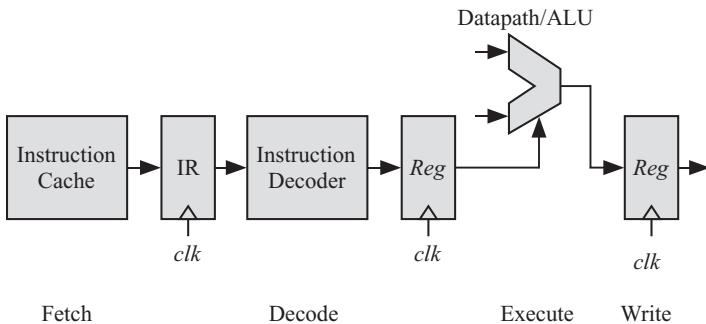

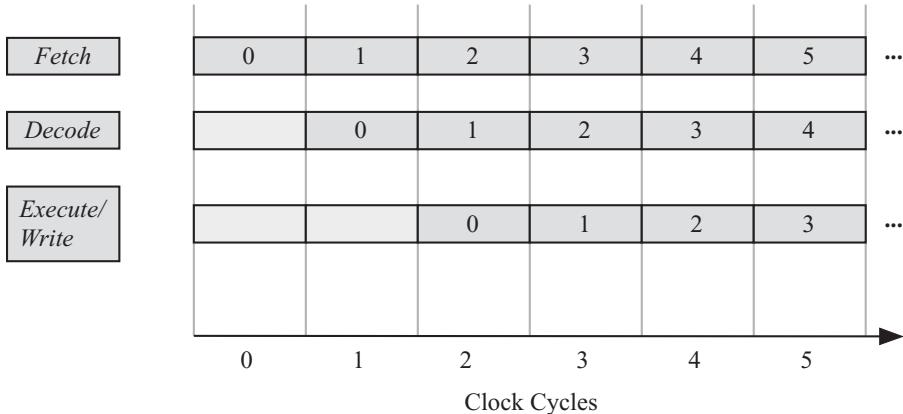

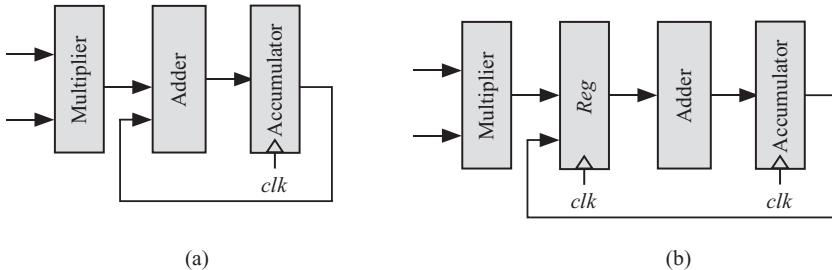

*Chapter 2* discusses the techniques used to enhance the performance of a single computer such as increasing the clock frequency, parallelizing the arithmetic and logic unit (ALU) structure, pipelining, very long instruction word (VLIW), superscalar computing, and multithreading.

*Chapter 3* reviews the main types of parallel computers discussed here and includes shared memory, distributed memory, single instruction multiple data stream (SIMD), systolic processors, and multicore systems.

*Chapter 4* reviews shared-memory multiprocessor systems and discusses two main issues intimately related to them: cache coherence and process synchronization.

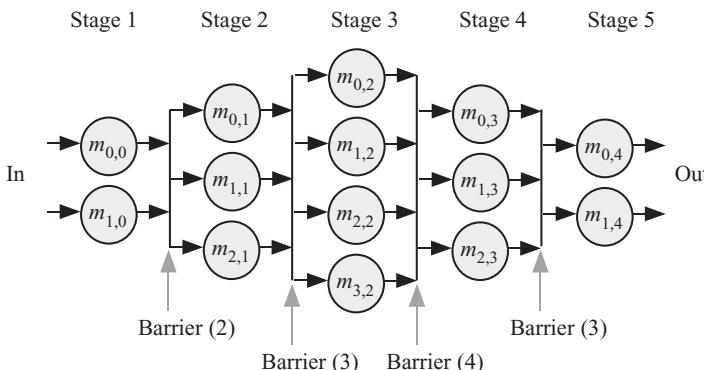

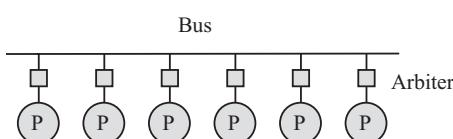

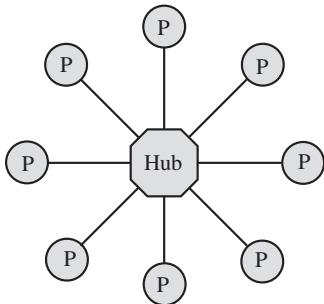

*Chapter 5* reviews the types of interconnection networks used in parallel processors. We discuss simple networks such as buses and move on to star, ring, and mesh topologies. More efficient networks such as crossbar and multistage interconnection networks are discussed.

*Chapter 6* reviews the concurrency platform software tools developed to help the programmer parallelize the application. Tools reviewed include Cilk++, OpenMP, and compute unified device architecture (CUDA). It is stressed, however, that these tools deal with simple data dependencies. It is the responsibility of the programmer

to ensure data integrity and correct timing of task execution. The techniques developed in this book help the programmer toward this goal for serial algorithms and for regular iterative algorithms.

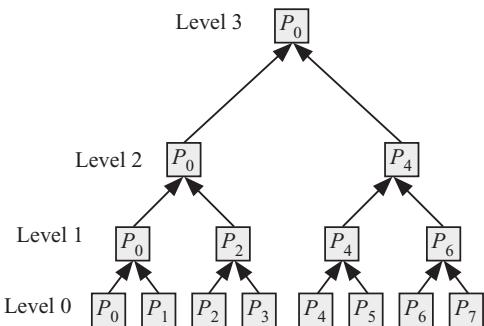

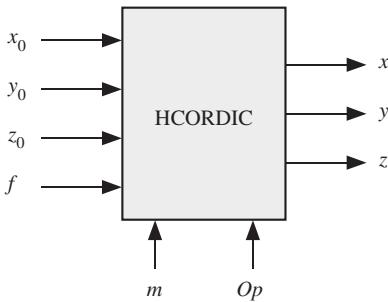

*Chapter 7* reviews the ad hoc techniques used to implement algorithms on parallel computers. These techniques include independent loop scheduling, dependent loop spreading, dependent loop unrolling, problem partitioning, and divide-and-conquer strategies. Pipelining at the algorithm task level is discussed, and the technique is illustrated using the coordinate rotation digital computer (CORDIC) algorithm.

*Chapter 8* deals with nonserial-parallel algorithms (NSPAs) that cannot be described as serial, parallel, or serial-parallel algorithms. NSPAs constitute the majority of general algorithms that are not apparently parallel or show a confusing task dependence pattern. The chapter discusses a formal, very powerful, and simple technique for extracting parallelism from an algorithm. The main advantage of the formal technique is that it gives us the best schedule for evaluating the algorithm on a parallel machine. The technique also tells us how many parallel processors are required to achieve maximum execution speedup. The technique enables us to extract important NSPA performance parameters such as work ( $W$ ), parallelism ( $P$ ), and depth ( $D$ ).

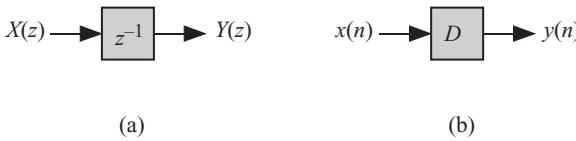

*Chapter 9* introduces the  $z$ -transform technique. This technique is used for studying the implementation of digital filters and multirate systems on different parallel processing machines. These types of applications are naturally studied in the  $z$ -domain, and it is only natural to study their software and hardware implementation using this domain.

*Chapter 10* discusses to construct the dependence graph associated with an iterative algorithm. This technique applies, however, to iterative algorithms that have one, two, or three indices at the most. The dependence graph will help us schedule tasks and automatically allocate them to software threads or hardware processors.

*Chapter 11* discusses an iterative algorithm analysis technique that is based on computation geometry and linear algebra concepts. The technique is general in the sense that it can handle iterative algorithms with more than three indices. An example is two-dimensional (2-D) or three-dimensional (3-D) digital filters. For such algorithms, we represent the algorithm as a convex hull in a multidimensional space and associate a dependence matrix with each variable of the algorithm. The null space of these matrices will help us derive the different parallel software threads and hardware processing elements and their proper timing.

*Chapter 12* explores different parallel processing structures for one-dimensional (1-D) finite impulse response (FIR) digital filters. We start by deriving possible hardware structures using the geometric technique of Chapter 11. Then, we explore possible parallel processing structures using the  $z$ -transform technique of Chapter 9.

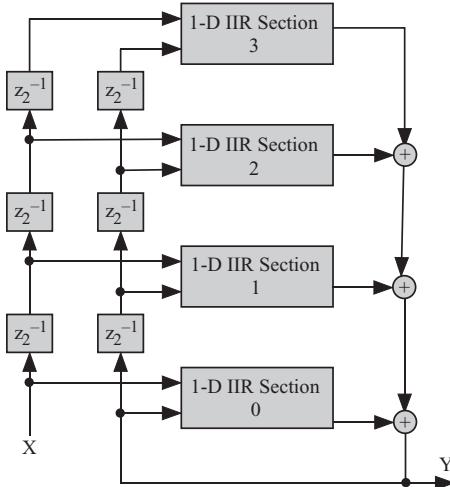

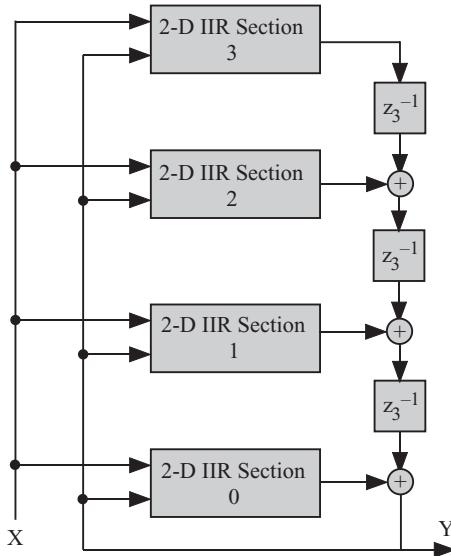

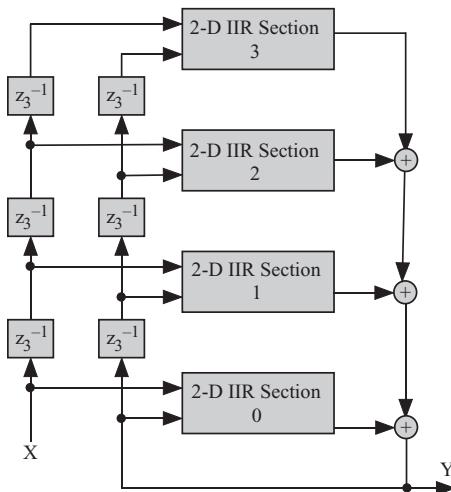

*Chapter 13* explores different parallel processing structures for 2-D and 3-D infinite impulse response (IIR) digital filters. We use the  $z$ -transform technique for this type of filter.

*Chapter 14* explores different parallel processing structures for multirate decimators and interpolators. These algorithms are very useful in many applications,

especially telecommunications. We use the dependence graph technique of Chapter 10 to derive different parallel processing structures.

*Chapter 15* explores different parallel processing structures for the pattern matching problem. We use the dependence graph technique of Chapter 10 to study this problem.

*Chapter 16* explores different parallel processing structures for the motion estimation algorithm used in video data compression. In order to delay with this complex algorithm, we use a hierarchical technique to simplify the problem and use the dependence graph technique of Chapter 10 to study this problem.

*Chapter 17* explores different parallel processing structures for finite-field multiplication over  $GF(2^m)$ . The multi-plication algorithm is studied using the dependence graph technique of Chapter 10.

*Chapter 18* explores different parallel processing structures for finite-field polynomial division over  $GF(2)$ . The division algorithm is studied using the dependence graph technique of Chapter 10.

*Chapter 19* explores different parallel processing structures for the fast Fourier transform algorithm. Pipeline techniques for implementing the algorithm are reviewed.

*Chapter 20* discusses solving systems of linear equations. These systems could be solved using direct and indirect techniques. The chapter discusses how to parallelize the forward substitution direct technique. An algorithm to convert a dense matrix to an equivalent triangular form using Givens rotations is also studied. The chapter also discusses how to parallelize the successive over-relaxation (SOR) indirect technique.

*Chapter 21* discusses solving partial differential equations using the finite difference method (FDM). Such equations are very important in many engineering and scientific applications and demand massive computation resources.

## **ACKNOWLEDGMENTS**

I wish to express my deep gratitude and thank Dr. M.W. El-Kharashi of Ain Shams University in Egypt for his excellent suggestions and encouragement during the preparation of this book. I also wish to express my personal appreciation of each of the following colleagues whose collaboration contributed to the topics covered in this book:

Dr. Esam Abdel-Raheem

*University of Windsor, Canada*

Dr. Turki Al-Somani

*Al-Baha University, Saudi Arabia*

Dr. Atef Ibrahim

*Electronics Research Institute, Egypt*

Dr. Mohamed Fayed

*Al-Azhar University, Egypt*

Mr. Brian McKinney

*ICEsoft, Canada*

Dr. Newaz Rafiq

*ParetoLogic, Inc., Canada*

Dr. Mohamed Rehan

*British University, Egypt*

Dr. Ayman Tawfik

*Ajman University, United Arab Emirates*

## **COMMENTS AND SUGGESTIONS**

This book covers a wide range of techniques and topics related to parallel computing. It is highly probable that it contains errors and omissions. Other researchers and/or practicing engineers might have other ideas about the content and organization of a book of this nature. We welcome receiving comments and suggestions for consideration. If you find any errors, we would appreciate hearing from you. We also welcome ideas for examples and problems (along with their solutions if possible) to include with proper citation.

Please send your comments and bug reports electronically to [fayez@uvic.ca](mailto:fayez@uvic.ca), or you can fax or mail the information to

Dr. FAYEZ GEBALI

Electrical and Computer Engineering Department

University of Victoria, Victoria, B.C., Canada V8W 3P6

Tel: 250-721-6509

Fax: 250-721-6052

# List of Acronyms

---

|             |                                           |

|-------------|-------------------------------------------|

| 1-D         | one-dimensional                           |

| 2-D         | two-dimensional                           |

| 3-D         | three-dimensional                         |

| ALU         | arithmetic and logic unit                 |

| AMP         | asymmetric multiprocessing system         |

| API         | application program interface             |

| ASA         | acyclic sequential algorithm              |

| ASIC        | application-specific integrated circuit   |

| ASMP        | asymmetric multiprocessor                 |

| CAD         | computer-aided design                     |

| CFD         | computational fluid dynamics              |

| CMP         | chip multiprocessor                       |

| CORDIC      | coordinate rotation digital computer      |

| CPI         | clock cycles per instruction              |

| CPU         | central processing unit                   |

| CRC         | cyclic redundancy check                   |

| CT          | computerized tomography                   |

| CUDA        | compute unified device architecture       |

| DAG         | directed acyclic graph                    |

| DBMS        | database management system                |

| DCG         | directed cyclic graph                     |

| DFT         | discrete Fourier transform                |

| DG          | directed graph                            |

| DHT         | discrete Hilbert transform                |

| DRAM        | dynamic random access memory              |

| DSP         | digital signal processing                 |

| FBMA        | full-search block matching algorithm      |

| FDM         | finite difference method                  |

| FDM         | frequency division multiplexing           |

| FFT         | fast Fourier transform                    |

| FIR         | finite impulse response                   |

| FLOPS       | floating point operations per second      |

| FPGA        | field-programmable gate array             |

| GF( $2^m$ ) | Galois field with $2^m$ elements          |

| GFLOPS      | giga floating point operations per second |

| GPGPU       | general purpose graphics processor unit   |

| GPU         | graphics processing unit                  |

|         |                                                       |

|---------|-------------------------------------------------------|

| HCORDIC | high-performance coordinate rotation digital computer |

| HDL     | hardware description language                         |

| HDTV    | high-definition TV                                    |

| HRCT    | high-resolution computerized tomography               |

| HTM     | hardware-based transactional memory                   |

| IA      | iterative algorithm                                   |

| IDHT    | inverse discrete Hilbert transform                    |

| IEEE    | Institute of Electrical and Electronic Engineers      |

| IIR     | infinite impulse response                             |

| ILP     | instruction-level parallelism                         |

| I/O     | input/output                                          |

| IP      | intellectual property modules                         |

| IP      | Internet protocol                                     |

| IR      | instruction register                                  |

| ISA     | instruction set architecture                          |

| JVM     | Java virtual machine                                  |

| LAN     | local area network                                    |

| LCA     | linear cellular automaton                             |

| LFSR    | linear feedback shift register                        |

| LHS     | left-hand side                                        |

| LSB     | least-significant bit                                 |

| MAC     | medium access control                                 |

| MAC     | multiply/accumulate                                   |

| MCAPI   | Multicore Communications Management API               |

| MIMD    | multiple instruction multiple data                    |

| MIMO    | multiple-input multiple-output                        |

| MIN     | multistage interconnection networks                   |

| MISD    | multiple instruction single data stream               |

| MIMD    | multiple instruction multiple data                    |

| MPI     | message passing interface                             |

| MRAPI   | Multicore Resource Management API                     |

| MRI     | magnetic resonance imaging                            |

| MSB     | most significant bit                                  |

| MTAPI   | Multicore Task Management API                         |

| NIST    | National Institute for Standards and Technology       |

| NoC     | network-on-chip                                       |

| NSPA    | nonserial-parallel algorithm                          |

| NUMA    | nonuniform memory access                              |

| NVCC    | NVIDIA C compiler                                     |

| OFDM    | orthogonal frequency division multiplexing            |

| OFDMA   | orthogonal frequency division multiple access         |

| OS      | operating system                                      |

| P2P     | peer-to-peer                                          |

| PA      | processor array                                       |

| PE      | processing element                                    |

|        |                                                                  |

|--------|------------------------------------------------------------------|

| PRAM   | parallel random access machine                                   |

| QoS    | quality of service                                               |

| RAID   | redundant array of inexpensive disks                             |

| RAM    | random access memory                                             |

| RAW    | read after write                                                 |

| RHS    | right-hand side                                                  |

| RIA    | regular iterative algorithm                                      |

| RTL    | register transfer language                                       |

| SE     | switching element                                                |

| SF     | switch fabric                                                    |

| SFG    | signal flow graph                                                |

| SIMD   | single instruction multiple data stream                          |

| SIMP   | single instruction multiple program                              |

| SISD   | single instruction single data stream                            |

| SLA    | service-level agreement                                          |

| SM     | streaming multiprocessor                                         |

| SMP    | symmetric multiprocessor                                         |

| SMT    | simultaneous multithreading                                      |

| SoC    | system-on-chip                                                   |

| SOR    | successive over-relaxation                                       |

| SP     | streaming processor                                              |

| SPA    | serial-parallel algorithm                                        |

| SPMD   | single program multiple data stream                              |

| SRAM   | static random access memory                                      |

| STM    | software-based transactional memory                              |

| TCP    | transfer control protocol                                        |

| TFLOPS | tera floating point operations per second                        |

| TLP    | thread-level parallelism                                         |

| TM     | transactional memory                                             |

| UMA    | uniform memory access                                            |

| VHDL   | very high-speed integrated circuit hardware description language |

| VHSIC  | very high-speed integrated circuit                               |

| VIQ    | virtual input queuing                                            |

| VLIW   | very long instruction word                                       |

| VLSI   | very large-scale integration                                     |

| VOQ    | virtual output queuing                                           |

| VRQ    | virtual routing/virtual queuing                                  |

| WAN    | wide area network                                                |

| WAR    | write after read                                                 |

| WAW    | write after write                                                |

| WiFi   | wireless fidelity                                                |

# Chapter 1

---

## Introduction

### 1.1 INTRODUCTION

The idea of a single-processor computer is fast becoming archaic and quaint. We now have to adjust our strategies when it comes to computing:

- It is impossible to improve computer performance using a single processor. Such processor would consume unacceptable power. It is more practical to use many simple processors to attain the desired performance using perhaps thousands of such simple computers [1].

- As a result of the above observation, if an application is not running fast on a single-processor machine, it will run even slower on new machines unless it takes advantage of parallel processing.

- Programming tools that can detect parallelism in a given algorithm have to be developed. An algorithm can show regular dependence among its variables or that dependence could be irregular. In either case, there is room for speeding up the algorithm execution provided that some subtasks can run concurrently while maintaining the correctness of execution can be assured.

- Optimizing future computer performance will hinge on good parallel programming at all levels: algorithms, program development, operating system, compiler, and hardware.

- The benefits of parallel computing need to take into consideration the number of processors being deployed as well as the communication overhead of processor-to-processor and processor-to-memory. Compute-bound problems are ones wherein potential speedup depends on the speed of execution of the algorithm by the processors. Communication-bound problems are ones wherein potential speedup depends on the speed of supplying the data to and extracting the data from the processors.

- Memory systems are still much slower than processors and their bandwidth is limited also to one word per read/write cycle.

- Scientists and engineers will no longer adapt their computing requirements to the available machines. Instead, there will be the practical possibility that they will adapt the computing hardware to solve their computing requirements.

This book is concerned with algorithms and the special-purpose hardware structures that execute them since software and hardware issues impact each other. Any software program ultimately runs and relies upon the underlying hardware support provided by the processor and the operating system. Therefore, we start this chapter with some definitions then move on to discuss some relevant design approaches and design constraints associated with this topic.

## 1.2 TOWARD AUTOMATING PARALLEL PROGRAMMING

We are all familiar with the process of algorithm implementation in software. When we write a code, we do not need to know the details of the target computer system since the compiler will take care of the details. However, we are steeped in thinking in terms of a single central processing unit (CPU) and sequential processing when we start writing the code or debugging the output. On the other hand, the processes of implementing algorithms in hardware or in software for parallel machines are more related than we might think. Figure 1.1 shows the main phases or layers of implementing an application in software or hardware using parallel computers. Starting at the top, *layer 5* is the application layer where the application or problem to be implemented on a parallel computing platform is defined. The specifications of inputs and outputs of the application being studied are also defined. Some input/output (I/O) specifications might be concerned with where data is stored and the desired timing relations of data. The results of this layer are fed to the lower layer to guide the algorithm development.

*Layer 4* is algorithm development to implement the application in question. The computations required to implement the application define the tasks of the algorithm and their interdependences. The algorithm we develop for the application might or might not display parallelism at this stage since we are traditionally used to linear execution of tasks. At this stage, we should not be concerned with task timing or task allocation to processors. It might be tempting to decide these issues, but this is counterproductive since it might preclude some potential parallelism. The result of this layer is a dependence graph, a directed graph (DG), or an adjacency matrix that summarize the task dependences.

*Layer 3* is the parallelization layer where we attempt to extract latent parallelism in the algorithm. This layer accepts the algorithm description from layer 4 and produces thread timing and assignment to processors for software implementation. Alternatively, this layer produces task scheduling and assignment to processors for custom hardware very large-scale integration (VLSI) implementation. The book concentrates on this layer, which is shown within the gray rounded rectangle in the figure.

*Layer 2* is the coding layer where the parallel algorithm is coded using a high-level language. The language used depends on the target parallel computing platform. The right branch in Fig. 1.1 is the case of mapping the algorithm on a general-purpose parallel computing platform. This option is really what we mean by *parallel programming*. Programming parallel computers is facilitated by what is called *concurrency platforms*, which are tools that help the programmer manage the threads and the timing of task execution on the processors. Examples of concurrency platforms include Cilk++, openMP, or compute unified device architecture (CUDA), as will be discussed in Chapter 6.

The left branch in Fig. 1.1 is the case of mapping the algorithm on a custom parallel computer such as systolic arrays. The programmer uses hardware description language (HDL) such as Verilog or very high-speed integrated circuit hardware (VHDL).

**Figure 1.1** The phases or layers of implementing an application in software or hardware using parallel computers.

*Layer 1* is the realization of the algorithm or the application on a parallel computer platform. The realization could be using multithreading on a parallel computer platform or it could be on an application-specific parallel processor system using application-specific integrated circuits (ASICs) or field-programmable gate array (FPGA).

So what do we mean by automatic programming of parallel computers? At the moment, we have automatic serial computer programming. The programmer writes a code in a high-level language such as C, Java, or FORTRAN, and the code is compiled without further input from the programmer. More significantly, the programmer does not need to know the hardware details of the computing platform. Fast code could result even if the programmer is unaware of the memory hierarchy, CPU details, and so on.

Does this apply to parallel computers? We have parallelizing compilers that look for simple loops and spread them among the processors. Such compilers could easily tackle what is termed *embarrassingly parallel algorithms* [2, 3]. Beyond that, the programmer must have intimate knowledge of how the processors interact among each and when the algorithm tasks are to be executed.

## 1.3 ALGORITHMS

The *IEEE Standard Dictionary of Electrical and Electronics Terms* defines an algorithm as “A prescribed set of well-defined rules or processes for the solution of a problem in a finite number of steps” [4]. The tasks or processes of an algorithm are interdependent in general. Some tasks can run concurrently in parallel and some must run serially or sequentially one after the other. According to the above definition, any algorithm is composed of a serial part and a parallel part. In fact, it is very hard to say that one algorithm is serial while the other is parallel except in extreme trivial cases. Later, we will be able to be more quantitative about this. If the number of tasks of the algorithm is  $W$ , then we say that the *work* associated with the algorithm is  $W$ .

The basic components defining an algorithm are

1. the different tasks,

2. the dependencies among the tasks where a task output is used as another task’s input,

3. the set of primary inputs needed by the algorithm, and

4. the set of primary outputs produced by the algorithm.

### 1.3.1 Algorithm DG

Usually, an algorithm is graphically represented as a DG to illustrate the data dependencies among the algorithm tasks. We use the DG to describe our algorithm in preference to the term “dependence graph” to highlight the fact that the algorithm

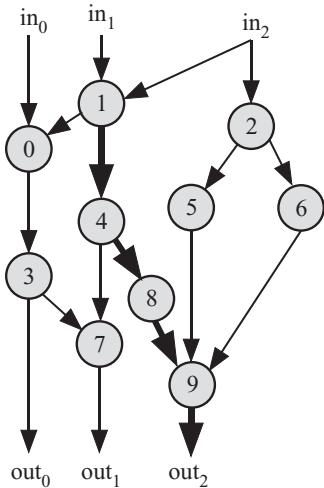

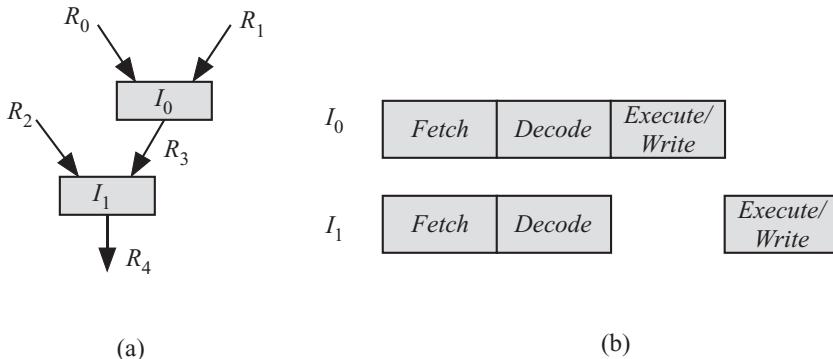

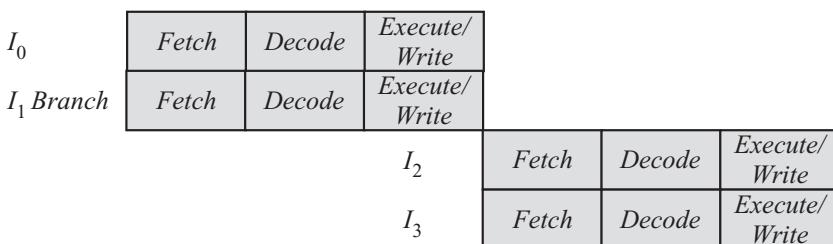

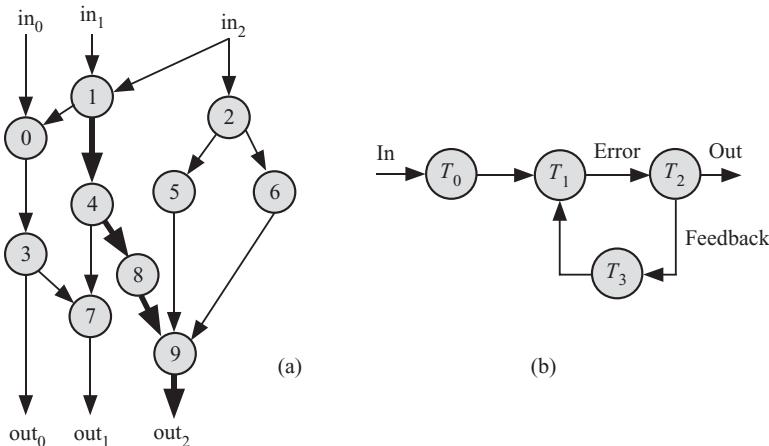

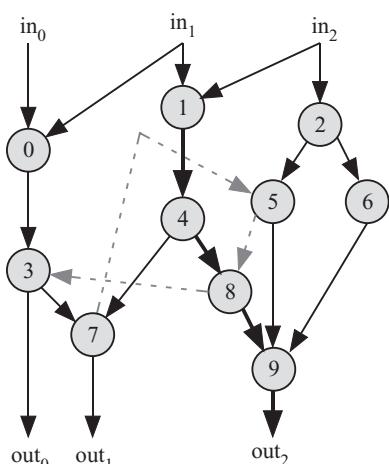

**Figure 1.2** Example of a directed acyclic graph (DAG) for an algorithm.

variables flow as data between the tasks as indicated by the arrows of the DG. On the other hand, a dependence graph is a graph that has no arrows at its edges, and it becomes hard to figure out the data dependencies.

**Definition 1.1** A dependence graph is a set of nodes and edges. The nodes represent the tasks to be done by the algorithm and the edges represent the data used by the tasks. This data could be input, output, or internal results.

Note that the edges in a dependence graph are undirected since an edge connecting two nodes does not indicate any input or output data dependency. An edge merely shows all the nodes that share a certain instance of the algorithm variable. This variable could be input, output, or I/O representing intermediate results.

**Definition 1.2** A DG is a set of nodes and directed edges. The nodes represent the tasks to be done by the algorithm, and the directed edges represent the data dependencies among the tasks. The start of an edge is the output of a task and the end of an edge is the input to the task.

**Definition 1.3** A directed acyclic graph (DAG) is a DG that has no cycles or loops.

Figure 1.2 shows an example of representing an algorithm by a DAG. A DG or DAG has three types of edges depending on the sources and destinations of the edges.

**Definition 1.4** An input edge in a DG is one that terminates on one or more nodes but does not start from any node. It represents one of the algorithm inputs.

Referring to Fig. 1.2, we note that the algorithm has three input edges that represent the inputs  $in_0$ ,  $in_1$ , and  $in_2$ .

**Definition 1.5** An output edge in a DG is one that starts from a node but does not terminate on any other node. It represents one of the algorithm outputs.

Referring to Fig. 1.2, we note that the algorithm has three output edges that represent the outputs  $\text{out}_0$ ,  $\text{out}_1$ , and  $\text{out}_2$ .

**Definition 1.6** An internal edge in a DG is one that starts from a node and terminate one or more nodes. It represents one of the algorithm internal variables.

**Definition 1.7** An input node in a DG is one whose incoming edges are all input edges.

Referring to Fig. 1.2, we note that nodes 0, 1, and 2 represent input nodes. The tasks associated with these nodes can start immediately after the inputs are available.

**Definition 1.8** An output node in a DG is whose outgoing edges are all output edges.

Referring to Fig. 1.2, we note that nodes 7 and 9 represent output nodes. Node 3 in the graph of Fig. 1.2 is not an output node since one of its outgoing edges is an internal edge terminating on node 7.

**Definition 1.9** An internal node in a DG is one that has at least one incoming internal edge and at least one outgoing internal edge.

### 1.3.2 Algorithm Adjacency Matrix $\mathbf{A}$

An algorithm could also be represented algebraically as an *adjacency matrix*  $\mathbf{A}$ . Given  $W$  nodes/tasks, we define the 0–1 adjacency matrix  $\mathbf{A}$ , which is a square  $W \times W$  matrix defined so that element  $a(i, j) = 1$  indicates that node  $i$  depends on the output from node  $j$ . The source node is  $j$  and the destination node is  $i$ . Of course, we must have  $a(i, i) = 0$  for all values of  $0 \leq i < W$  since node  $i$  does not depend on its own output (self-loop), and we assumed that we do not have any loops. The definition of the adjacency matrix above implies that this matrix is asymmetric. This is because if node  $i$  depends on node  $j$ , then the reverse is not true when loops are not allowed.

As an example, the adjacency matrix for the algorithm in Fig. 1.2 is given by

$$\mathbf{A} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \end{bmatrix}. \quad (1.1)$$

Matrix  $\mathbf{A}$  has some interesting properties related to our topic. An input node  $i$  is associated with row  $i$ , whose elements are all zeros. An output node  $j$  is associated with column  $j$ , whose elements are all zeros. We can write

$$\text{Input node } i \Rightarrow \sum_{j=0}^{W-1} a(i, j) = 0 \quad (1.2)$$

$$\text{Output node } j \Rightarrow \sum_{i=0}^{W-1} a(i, j) = 0. \quad (1.3)$$

All other nodes are internal nodes. Note that all the elements in rows 0, 1, and 2 are all zeros since nodes 0, 1, and 2 are input nodes. This is indicated by the bold entries in these three rows. Note also that all elements in columns 7 and 9 are all zeros since nodes 7 and 9 are output nodes. This is indicated by the bold entries in these two columns. All other rows and columns have one or more nonzero elements to indicate internal nodes. If node  $i$  has element  $a(i, j) = 1$ , then we say that node  $j$  is a parent of node  $i$ .

### 1.3.3 Classifying Algorithms Based On Task Dependences

Algorithms can be broadly classified based on task dependences:

1. Serial algorithms

2. Parallel algorithms

3. Serial-parallel algorithms (SPAs)

4. Nonserial-parallel algorithms (NSPAs)

5. Regular iterative algorithms (RIAs)

The last category could be thought of as a generalization of SPAs. It should be mentioned that the level of data or task granularity can change the algorithm from one class to another. For example, adding two matrices could be an example of a serial algorithm if our basic operation is adding two matrix elements at a time. However, if we add corresponding rows on different computers, then we have a row-based parallel algorithm.

We should also mention that some algorithms can contain other types of algorithms within their tasks. The simple matrix addition example serves here as well. Our parallel matrix addition algorithm adds pairs of rows at the same time on different processors. However, each processor might add the rows one element at a time, and thus, the tasks of the parallel algorithm represent serial row add algorithms. We discuss these categories in the following subsections.

### 1.3.4 Serial Algorithms

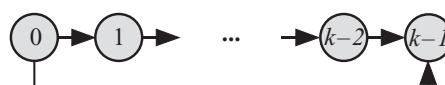

A serial algorithm is one where the tasks must be performed in series one after the other due to their data dependencies. The DG associated with such an algorithm looks

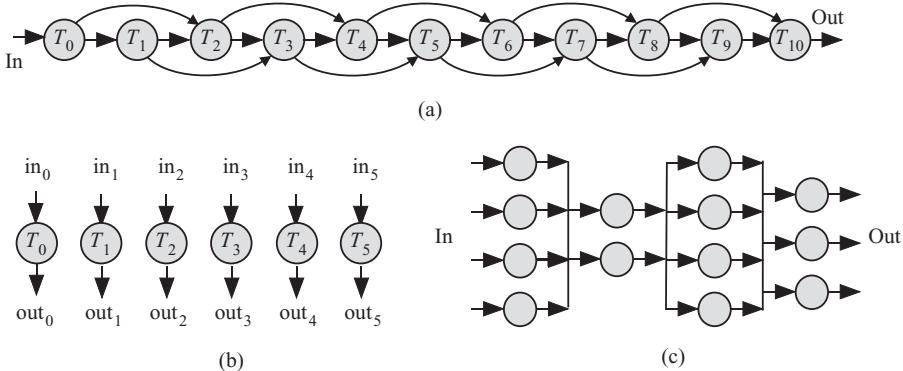

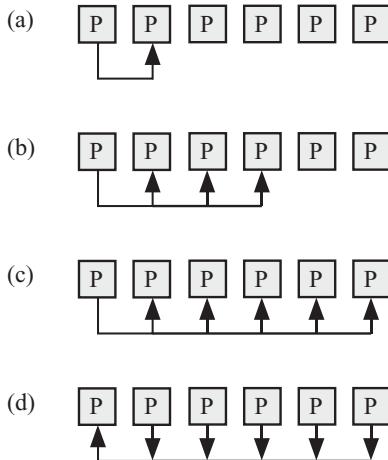

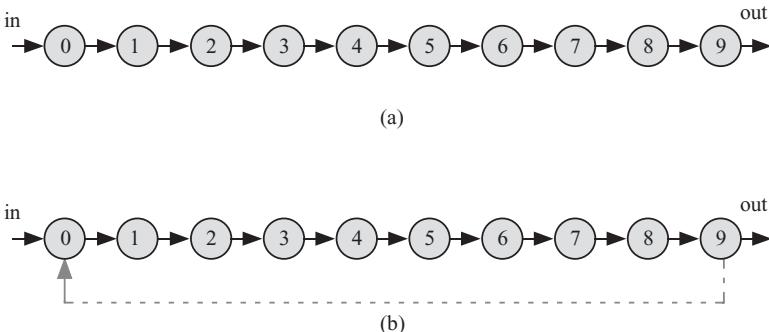

**Figure 1.3** Example of serial, parallel, and serial-parallel algorithms. (a) Serial algorithm. (b) Parallel algorithm. (c) Serial-parallel algorithm.

like a long string or queue of dependent tasks. Figure 1.3a shows an example of a serial algorithm. The algorithm shown is for calculating Fibonacci numbers. To calculate Fibonacci number  $n_{10}$ , task  $T_{10}$  performs the following simple calculation:

$$n_{10} = n_8 + n_9, \quad (1.4)$$

with  $n_0 = 0$  and  $n_1 = 1$  given as initial conditions. Clearly, we can find a Fibonacci number only after the preceding two Fibonacci numbers have been calculated.

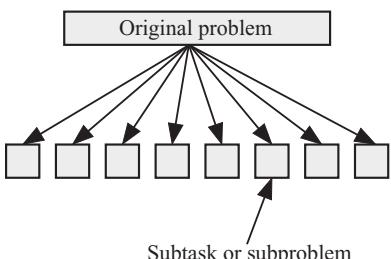

### 1.3.5 Parallel Algorithms

A parallel algorithm is one where the tasks could all be performed in parallel at the same time due to their data independence. The DG associated with such an algorithm looks like a wide row of independent tasks. Figure 1.3b shows an example of a parallel algorithm. A simple example of such a purely parallel algorithm is a web server where each incoming request can be processed independently from other requests. Another simple example of parallel algorithms is multitasking in operating systems where the operating system deals with several applications like a web browser, a word processor, and so on.

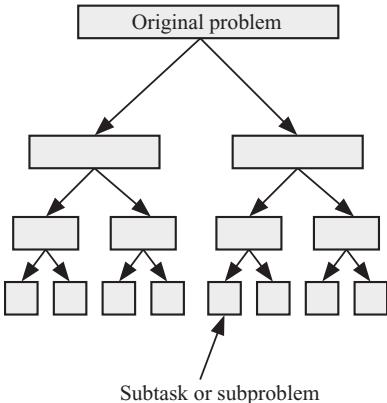

### 1.3.6 SPAs

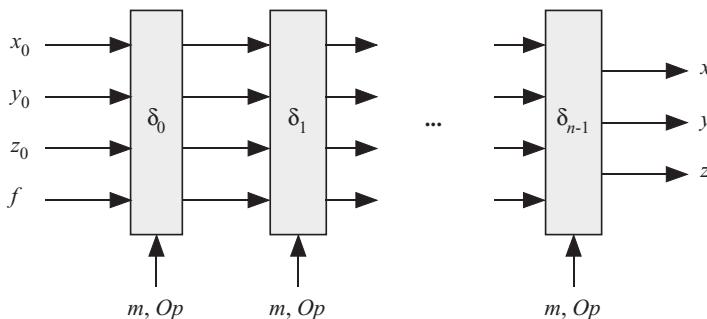

An SPA is one where tasks are grouped in stages such that the tasks in each stage can be executed concurrently in parallel and the stages are executed sequentially. An SPA becomes a parallel algorithm when the number of stages is one. A serial-parallel algorithm also becomes a serial algorithm when the number of tasks in each stage is one. Figure 1.3c shows an example of an SPA. An example of an SPA is the CORDIC algorithm [5–8]. The algorithm requires  $n$  iterations and at iteration  $i$ , three operations are performed:

$$\begin{aligned}

x_{i+1} &= x_i + m y_i \delta_i \\

y_{i+1} &= y_i - x_i \delta_i \\

z_{i+1} &= z_i + \theta_i,

\end{aligned} \tag{1.5}$$

where  $x$ ,  $y$ , and  $z$  are the data to be updated at each iteration.  $\delta_i$  and  $\theta_i$  are iteration constants that are stored in lookup tables. The parameter  $m$  is a control parameter that determines the type of calculations required. The variable  $\theta_i$  is determined before the start of each iteration. The algorithm performs other operations during each iteration, but we are not concerned about this here. More details can be found in Chapter 7 and in the cited references.

### 1.3.7 NSPAs

An NSPA does not conform to any of the above classifications. The DG for such an algorithm has no pattern. We can further classify NSPA into two main categories based on whether their DG contains cycles or not. Therefore, we can have two types of graphs for NSPA:

1. DAG

2. Directed cyclic graph (DCG)

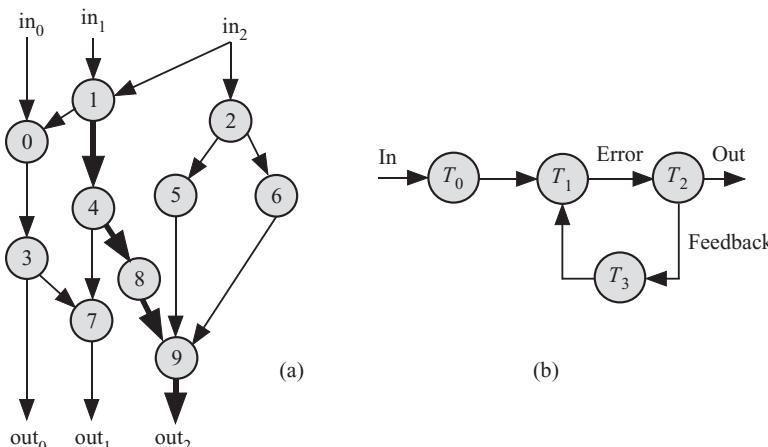

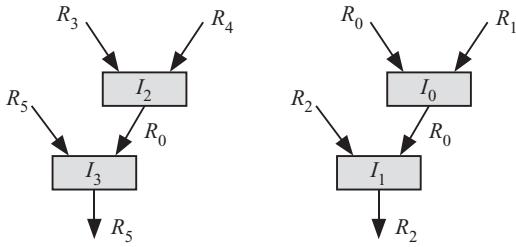

Figure 1.4a is an example of a DAG algorithm and Fig. 1.4b is an example of a DCG algorithm. The DCG is most commonly encountered in discrete time feedback control systems. The input is supplied to task  $T_0$  for prefiltering or input signal conditioning. Task  $T_1$  accepts the conditioned input signal and the conditioned feedback output signal. The output of task  $T_1$  is usually referred to as the error signal, and this signal is fed to task  $T_2$  to produce the output signal.

**Figure 1.4** Example directed graphs for nonserial-parallel algorithms. (a) Directed acyclic graph (DAG). (b) Directed cyclic graph (DCG).

The NSPA graph is characterized by two types of constructs: the *nodes*, which describe the tasks comprising the algorithm, and the *directed edges*, which describe the direction of data flow among the tasks. The lines exiting a node represent an output, and when they enter a node, they represent an input. If task  $T_i$  produces an output that is used by task  $T_j$ , then we say that  $T_j$  depends on  $T_i$ . On the graph, we have an arrow from node  $i$  to node  $j$ .

The DG of an algorithm gives us three important properties:

1. *Work (W)*, which describes the amount of processing work to be done to complete the algorithm

2. *Depth (D)*, which is also known as the *critical path*. Depth is defined as the maximum path length between any input node and any output node.

3. *Parallelism (P)*, which is also known as the *degree of parallelism* of the algorithm. Parallelism is defined as the maximum number of nodes that can be processed in parallel. The maximum number of parallel processors that could be active at any given time will not exceed  $B$  since anymore processors will not find any tasks to execute.

A more detailed discussion of these properties and how an algorithm can be mapped onto a parallel computer is found in Chapter 8.

### 1.3.8 RIAs

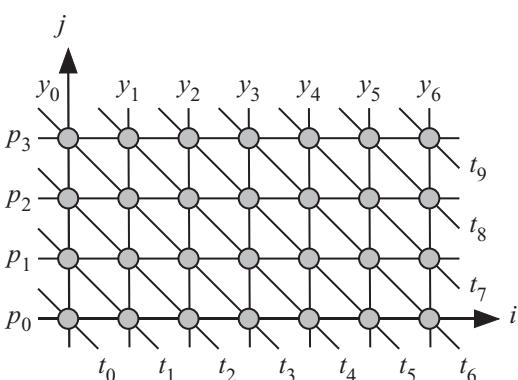

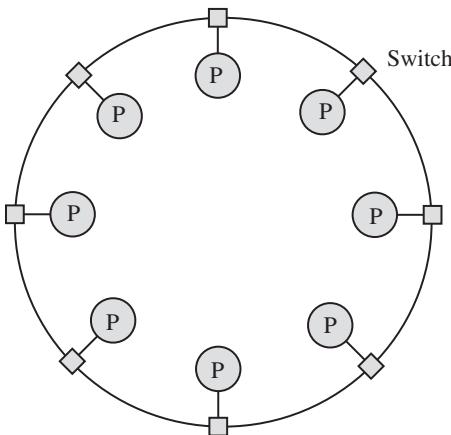

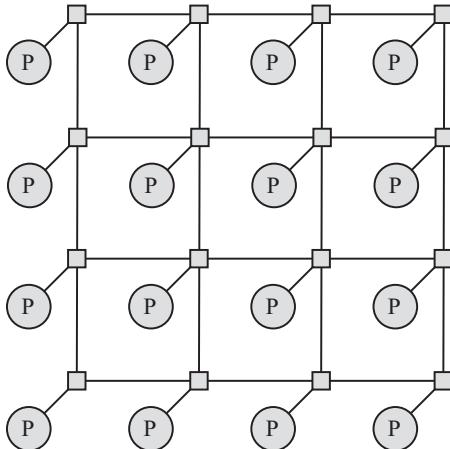

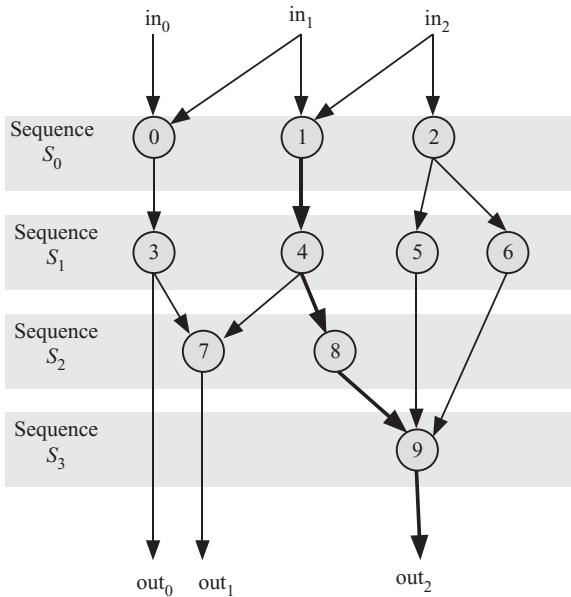

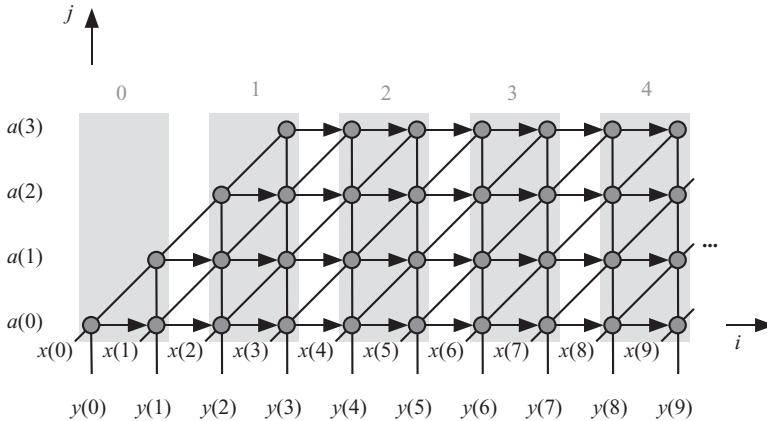

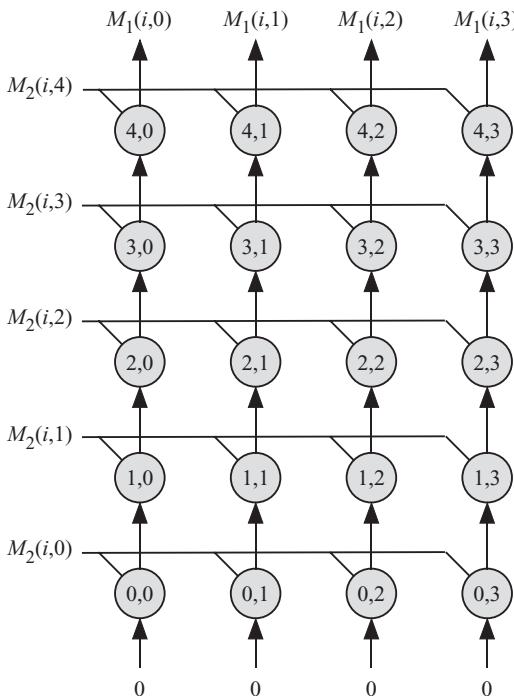

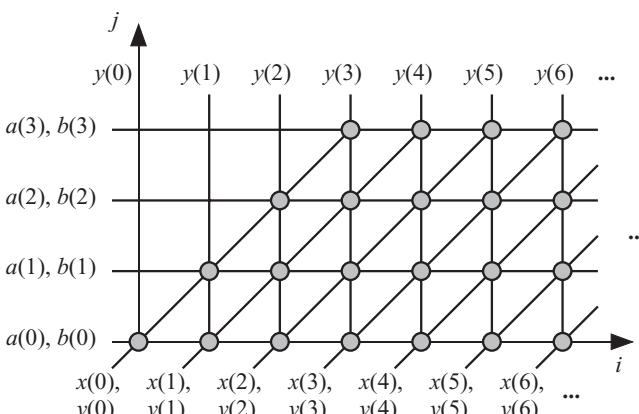

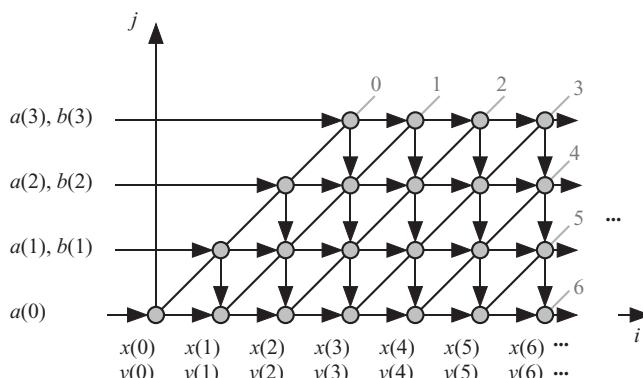

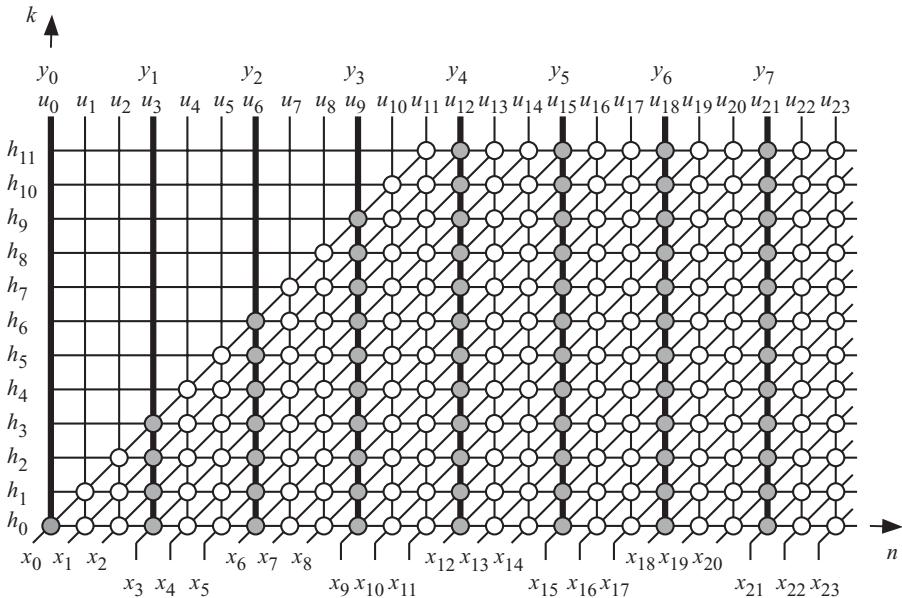

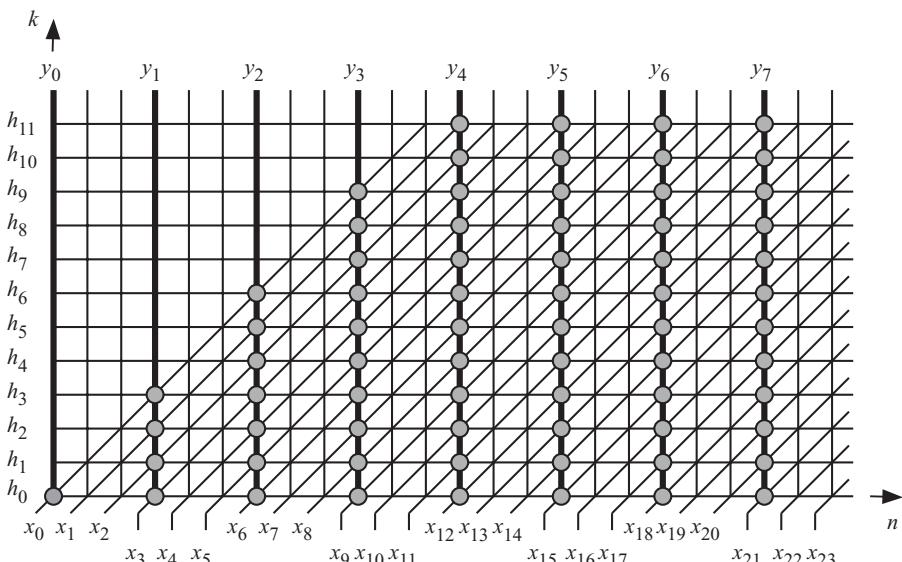

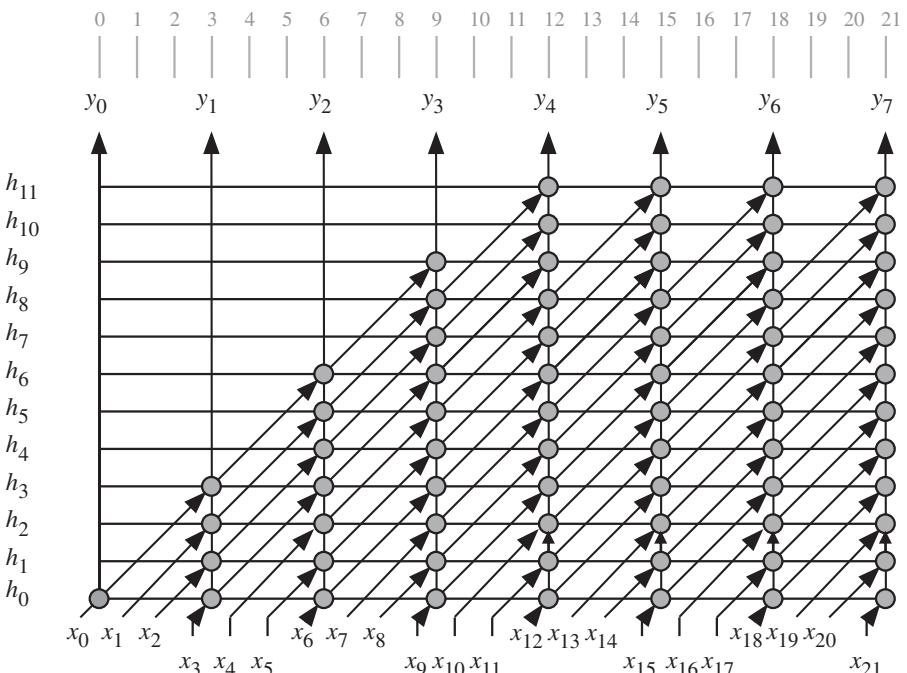

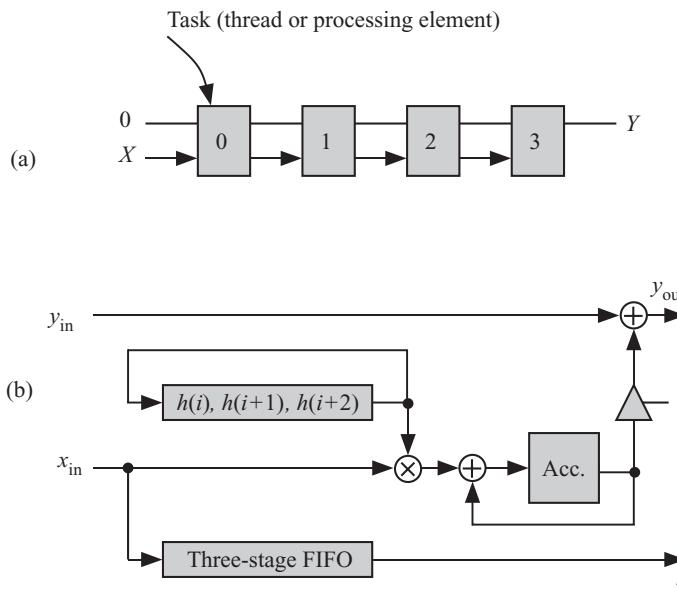

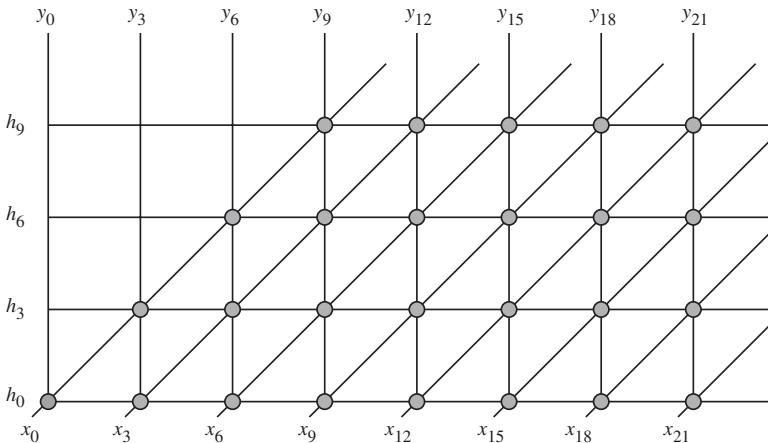

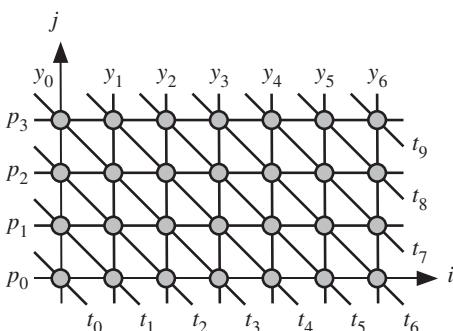

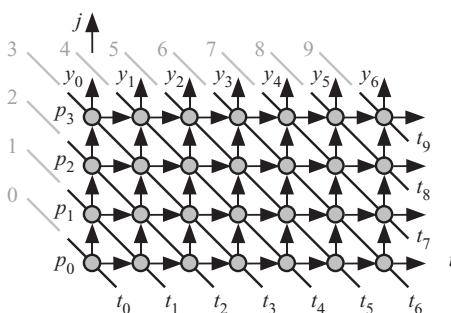

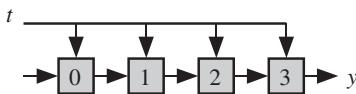

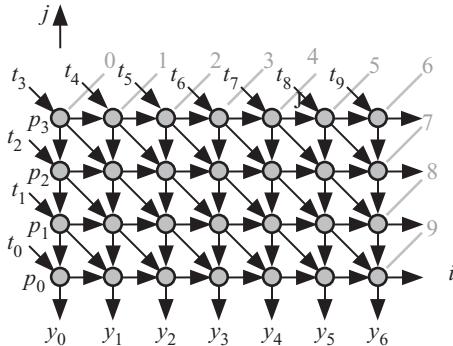

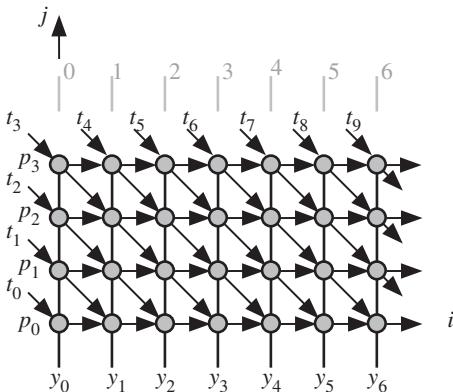

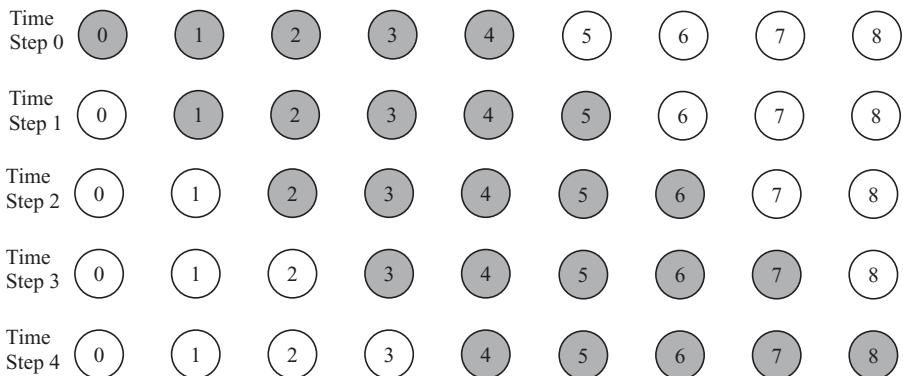

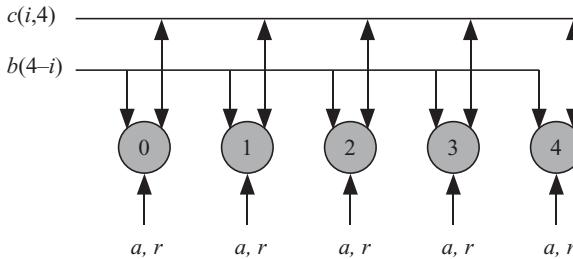

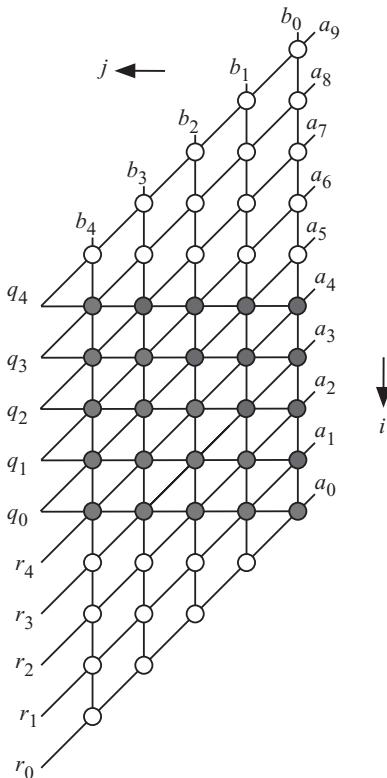

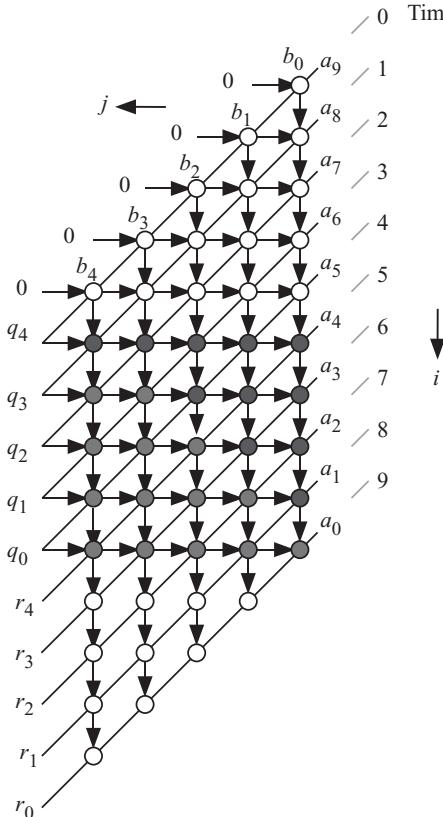

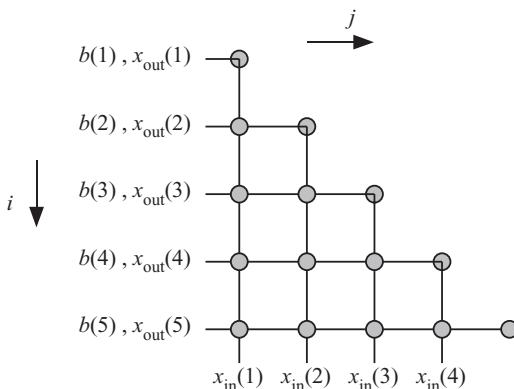

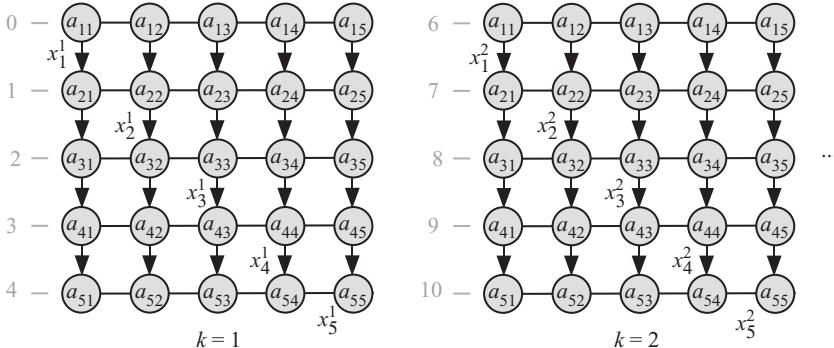

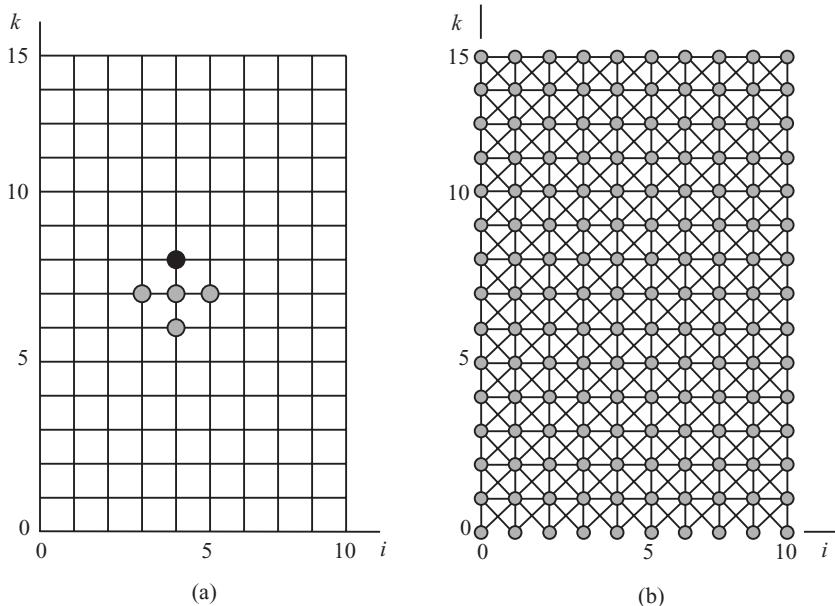

Karp et al. [9, 10] introduced the concept of RIA. This class of algorithms deserves special attention because they are found in algorithms from diverse fields such as signal, image and video processing, linear algebra applications, and numerical simulation applications that can be implemented in grid structures. Figure 1.5 shows the *dependence graph* of a RIA. The example is for pattern matching algorithm. Notice that for a RIA, we do not draw a DAG; instead, we use the dependence graph concept.

**Figure 1.5** Dependence graph of a RIA for the pattern matching algorithm.

A dependence graph is like a DAG except that the links are not directed and the graph is obtained according to the methodology explained in Chapters 9, 10, and 11.

In a RIA, the dependencies among the tasks show a fixed pattern. It is a trivial problem to parallelize a serial algorithm, a parallel algorithm, or even an SPA. It is not trivial to explore the possible parallelization options of a RIA. In fact, Chapters 9–11 are dedicated to just exploring the parallelization of this class of algorithms.

A simple example of a RIA is the matrix–matrix multiplication algorithm given by Algorithm 1.1.

---

**Algorithm 1.1** Matrix–matrix multiplication algorithm.

---

**Require:** Input: matrices  $A$  and  $B$

```

1: for  $i = 0 : I - 1$  do

2:   for  $j = 0 : J - 1$  do

3:      $temp = 0$

4:     for  $k = 0 : K - 1$  do

5:        $temp = temp + A(i, k) \times B(k, j)$

6:     end for

7:      $C(i, j) = temp$

8:   end for

9: end for

10: RETURN  $C$

```

---

The variables in the RIA described by Algorithm 1.1 show regular dependence on the algorithm indices  $i$ ,  $j$ , and  $k$ . Traditionally, such algorithms are studied using the dependence graph technique, which shows the links between the different tasks to be performed [10–12]. The dependence graph is attractive when the number of algorithm indices is 1 or 2. We have three indices in our matrix–matrix multiplication algorithm. It would be hard to visualize such an algorithm using a three-dimensional (3-D) graph. For higher dimensionality algorithms, we use more formal techniques as will be discussed in this book. Chapters 9–11 are dedicated to studying such algorithms.

### 1.3.9 Implementing Algorithms on Parallel Computing

The previous subsections explained different classes of algorithms based on the dependences among the algorithm tasks. We ask in this section how to implement these different algorithms on parallel computing platforms either in hardware or in software. This is referred to as parallelizing an algorithm. The parallelization strategy depends on the type of algorithm we are dealing with.

### ***Serial Algorithms***

Serial algorithms, as exemplified by Fig. 1.3a, cannot be parallelized since the tasks must be executed sequentially. The only parallelization possible is when each task is broken down into parallelizable subtasks. An example is to perform bit-parallel add/multiply operations.

### ***Parallel Algorithms***

Parallel algorithms, as exemplified by Fig. 1.3b, are easily parallelized since all the tasks can be executed in parallel, provided there are enough computing resources.

### ***SPAs***

SPAs, as exemplified by Fig. 1.3c, are parallelized by assigning each task in a stage to a software thread or hardware processing element. The stages themselves cannot be parallelized since they are serial in nature.

### ***NSPAs***

Techniques for parallelizing NSPAs will be discussed in Chapter 8.

### ***RIAs***

Techniques for parallelizing RIAs will be discussed in Chapters 9–11.

## **1.4 PARALLEL COMPUTING DESIGN CONSIDERATIONS**

This section discusses some of the important aspects of the design of parallel computing systems. The design of a parallel computing system requires considering many design options. The designer must choose a basic *processor architecture* that is capable of performing the contemplated tasks. The processor could be a simple element or it could involve a superscalar processor running a multithreaded operating system.

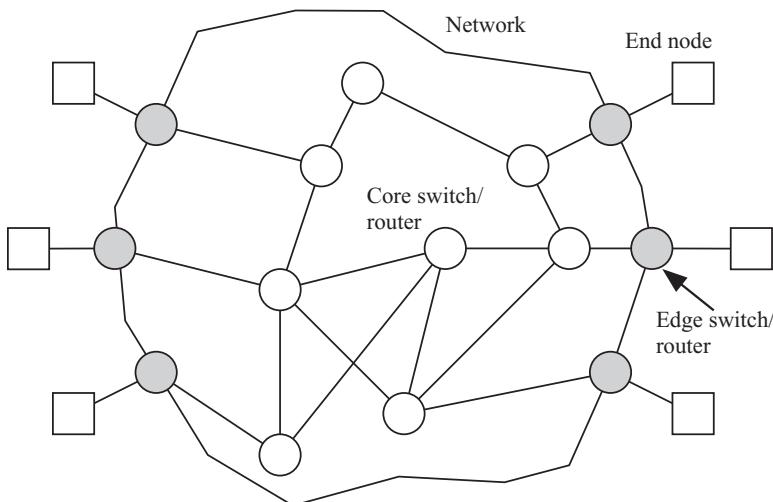

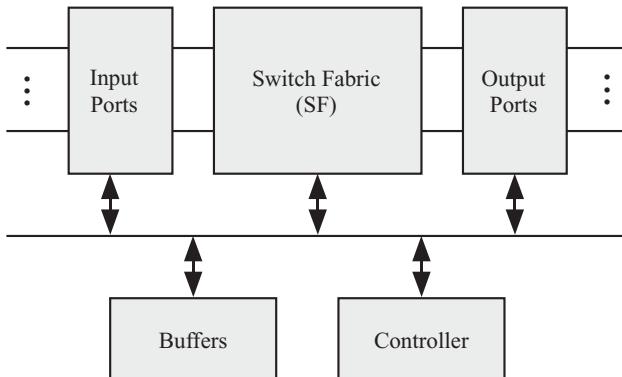

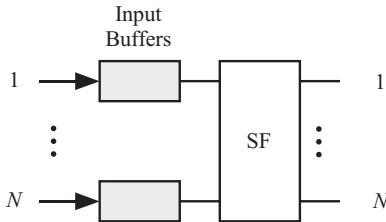

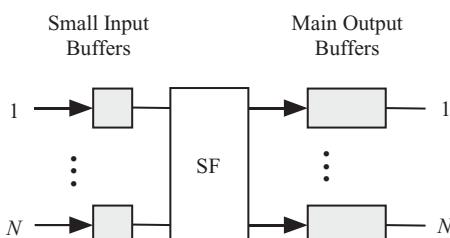

The processors must communicate among themselves using some form of an *interconnection network*. This network might prove to be a bottleneck if it cannot support simultaneous communication between arbitrary pairs of processors. Providing the links between processors is like providing physical channels in telecommunications. How data are exchanged must be specified. A bus is the simplest form of interconnection network. Data are exchanged in the form of words, and a system clock informs the processors when data are valid. Nowadays, buses are being replaced by *networks-on-chips* (NoC) [13]. In this architecture, data are exchanged on the chip in the form of *packets* and are routed among the chip modules using *routers*.

Data and programs must be stored in some form of *memory system*, and the designer will then have the option of having several memory modules shared among

the processors or of dedicating a memory module to each processor. When processors need to share data, mechanisms have to be devised to allow reading and writing data in the different memory modules. The order of reading and writing will be important to ensure data integrity. When a shared data item is updated by one processor, all other processors must be somehow informed of the change so they use the appropriate data value.

Implementing the tasks or programs on a parallel computer involves several design options also. *Task partitioning* breaks up the original program or application into several segments to be allocated to the processors. The level of partitioning determines the workload allocated to each processor. *Coarse grain partitioning* allocates large segments to each processor. *Fine grain partitioning* allocates smaller segments to each processor. These segments could be in the form of separate *software processes* or *threads*. The programmer or the compiler might be the two entities that decide on this partitioning. The programmer or the operating system must ensure proper *synchronization* among the executing tasks so as to ensure program correctness and data integrity.

## **1.5 PARALLEL ALGORITHMS AND PARALLEL ARCHITECTURES**

Parallel algorithms and parallel architectures are closely tied together. We cannot think of a parallel algorithm without thinking of the parallel hardware that will support it. Conversely, we cannot think of parallel hardware without thinking of the parallel software that will drive it. Parallelism can be implemented at different levels in a computing system using hardware and software techniques:

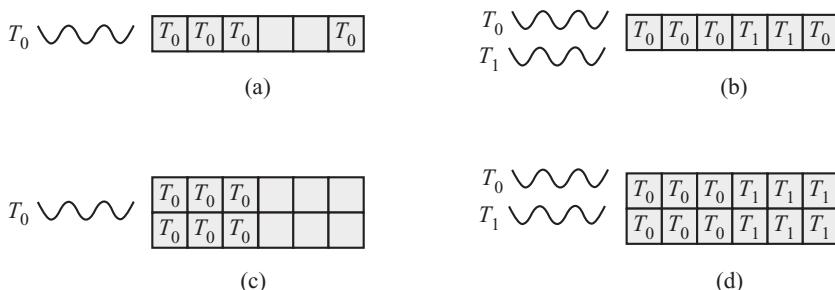

1. *Data-level parallelism*, where we simultaneously operate on multiple bits of a datum or on multiple data. Examples of this are bit-parallel addition multiplication and division of binary numbers, vector processor arrays and systolic arrays for dealing with several data samples. This is the subject of this book.

2. *Instruction-level parallelism (ILP)*, where we simultaneously execute more than one instruction by the processor. An example of this is use of instruction pipelining.

3. *Thread-level parallelism (TLP)*. A thread is a portion of a program that shares processor resources with other threads. A thread is sometimes called a light-weight process. In TLP, multiple software threads are executed simultaneously on one processor or on several processors.

4. *Process-level parallelism*. A process is a program that is running on the computer. A process reserves its own computer resources such as memory space and registers. This is, of course, the classic multitasking and time-sharing computing where several programs are running simultaneously on one machine or on several machines.

## 1.6 RELATING PARALLEL ALGORITHM AND PARALLEL ARCHITECTURE

The *IEEE Standard Dictionary of Electrical and Electronics Terms* [4] defines “parallel” for software as “simultaneous transfer, occurrence, or processing of the individual parts of a whole, such as the bits of a character and the characters of a word using separate facilities for the various parts.” So in that sense, we say an algorithm is parallel when two or more parts of the algorithms can be executed independently on hardware. Thus, the definition of a parallel algorithm presupposes availability of supporting hardware. This gives a hint that parallelism in software is closely tied to the hardware that will be executing the software code. Execution of the parts can be done using different threads or processes in the software or on different processors in the hardware. We can quickly identify a potentially parallel algorithm when we see the occurrence of “FOR” or “WHILE” loops in the code.

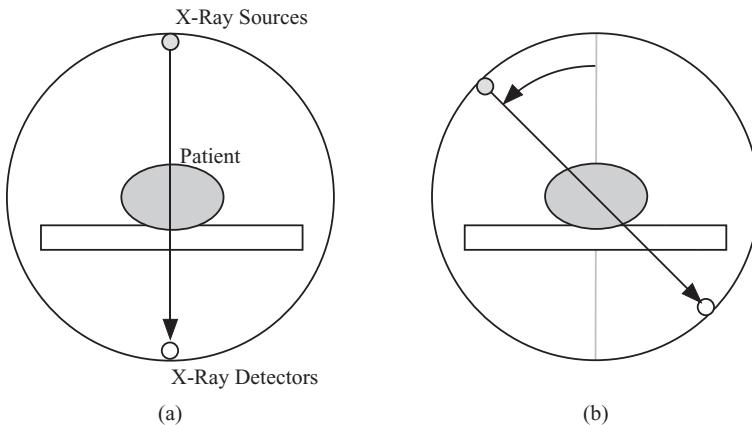

On the other hand, the definition of parallel architecture, according to *The IEEE Standard Dictionary of Electrical and Electronics Terms* [4], is “a multi-processor architecture in which parallel processing can be performed.” It is the job of the programmer, compiler, or operating system to supply the multiprocessor with tasks to keep the processors busy. We find ready examples of parallel algorithms in fields such as

- scientific computing, such as physical simulations, differential equations solvers, wind tunnel simulations, and weather simulation;

- computer graphics, such as image processing, video compression; and ray tracing; and,

- medical imaging, such as in magnetic resonance imaging (MRI) and computerized tomography (CT).

There are, however, equally large numbers of algorithms that are not recognizably parallel especially in the area of information technology such as online medical data, online banking, data mining, data warehousing, and database retrieval systems. The challenge is to develop computer architectures and software to speed up the different information technology applications.

## 1.7 IMPLEMENTATION OF ALGORITHMS: A TWO-SIDED PROBLEM

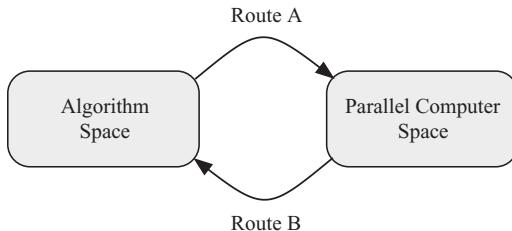

Figure 1.6 shows the issues we would like to deal with in this book. On the left is the space of algorithms and on the right is the space of parallel architectures that will execute the algorithms. Route A represents the case when we are given an algorithm and we are exploring possible parallel hardware or processor arrays that would correctly implement the algorithm according to some performance requirements and certain system constraints. In other words, the problem is given a parallel algorithm, what are the possible parallel processor architectures that are possible?

**Figure 1.6** The two paths relating parallel algorithms and parallel architectures.

Route B represents the classic case when we are given a parallel architecture or a multicore system and we explore the best way to implement a given algorithm on the system subject again to some performance requirements and certain system constraints. In other words, the problem is given a parallel architecture, how can we allocate the different tasks of the parallel algorithm to the different processors? This is the realm of parallel programming using the multithreading design technique. It is done by the application programmer, the software compiler, and the operating system.

Moving along routes A or B requires dealing with

1. *mapping* the tasks to different processors,

2. *scheduling* the execution of the tasks to conform to algorithm data dependency and data I/O requirements, and

3. *identifying* the data communication between the processors and the I/O.

## 1.8 MEASURING BENEFITS OF PARALLEL COMPUTING

We review in this section some of the important results and benefits of using parallel computing. But first, we identify some of the key parameters that we will be studying in this section.

### 1.8.1 Speedup Factor

The potential benefit of parallel computing is typically measured by the time it takes to complete a task on a single processor versus the time it takes to complete the same task on  $N$  parallel processors. The speedup  $S(N)$  due to the use of  $N$  parallel processors is defined by

$$S(N) = \frac{T_p(1)}{T_p(N)}, \quad (1.6)$$

where  $T_p(1)$  is the algorithm processing time on a single processor and  $T_p(N)$  is the processing time on the parallel processors. In an ideal situation, for a fully

parallelizable algorithm, and when the communication time between processors and memory is neglected, we have  $T_p(N) = T_p(1)/N$ , and the above equation gives

$$S(N) = N. \quad (1.7)$$

It is rare indeed to get this linear increase in computation domain due to several factors, as we shall see in the book.

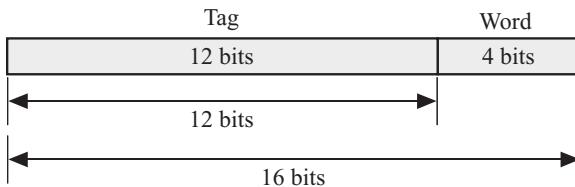

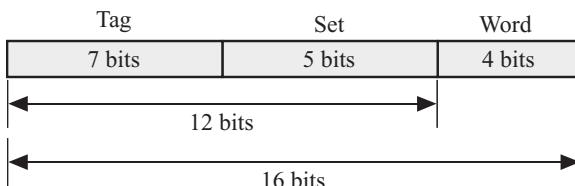

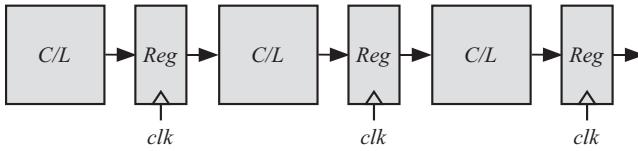

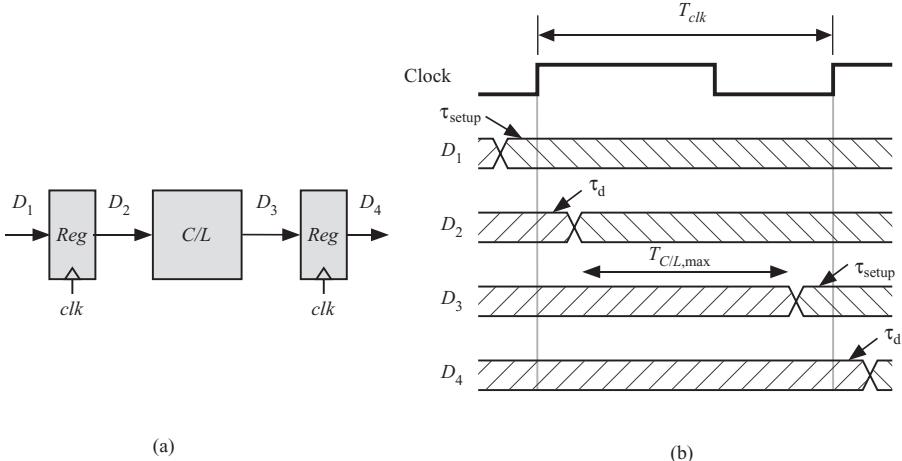

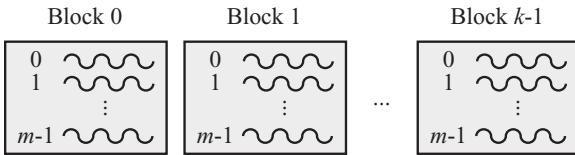

### 1.8.2 Communication Overhead